D'Kraaft vum s-r latch ze verstoen: eng Paart fir modern Elektronik

Latches sinn einfach digital Geräter déi e bëssen Informatioun stockéieren an dee Wäert halen bis et nei Input Signaler kritt.Si ginn an digitale Systemer benotzt fir binär Daten ze halen.Lancéiert ka mat verschiddenen Aarte vu Basislogikpatcher wéi an, oder nan, nand an nan an an och net katten.Esou Artikel kënnt dir déi néideg Geschicht a Funktioun aus der Lëscht, an d'Notzer vum S-r d'Stréckeren, als eng bescht Manéier zu kantal Simuits an hiren Uelegungsmëttel a se am Projeten a praktesch Routinistatioune gemaach.

Calalog

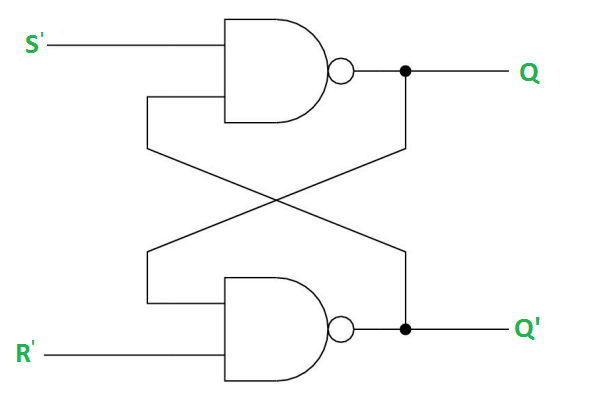

Bild 1: S-r Latch Circuit Diagramm

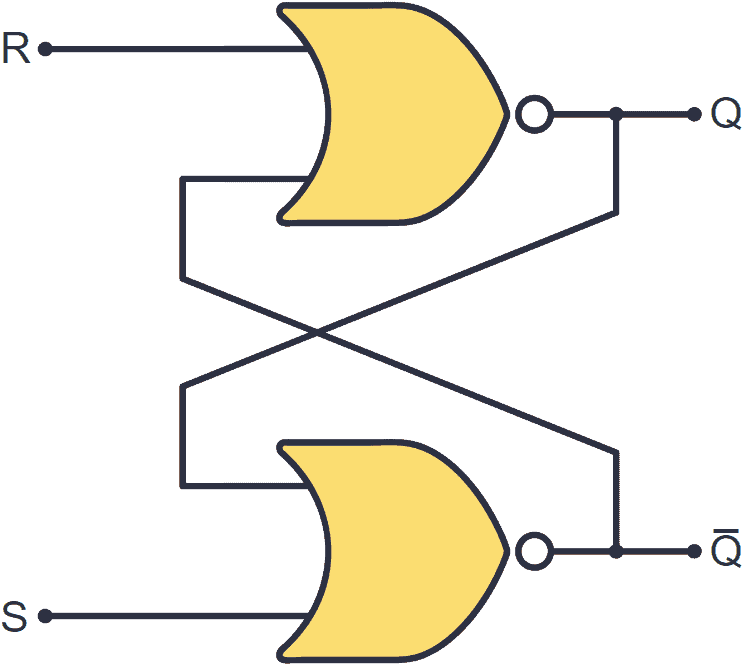

Struktur vum S-r Latch

De s-r (set-reset) latch, e Ecksteen an Digital Electronics, ass e bistableche Multiviibor.Et ass kapabel vun engem vun zwee ënnerscheede stabile Staaten onbestëmmt ouni extern Input ze halen.Dës Funktionalitéit renders de sr latch eng Haaptkomponent an der Erënnerungslagerung a wiesselt op eng aner elektronesch Apparater.

Strukturéiert ginn hien huet deenen zwee stéierenekt nach ofgezeechent ginn an net gestëmmt an engem Feedback lackene lackelt.Dëst spezifescht Arrangement ass wichteg zënter datt et d'Viraussetzunge fir d'Bestabilitéit ubitt.All Organisatioun vun Zielung ass direkt am Ufank ofginn, déi eng kontinuéierlech Lebo-Feedback ass, déi den Losst sech d'Entwécklung vun der Ludder ëmfréngen.

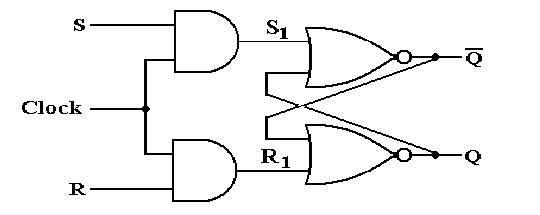

Bild 2: S-r Latch an der Auer Signal (CLK)

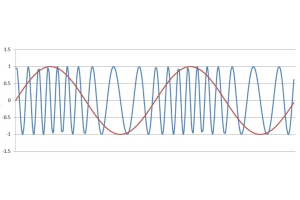

Ausbau vun der Basisdatei, deen de gatten SRC de GATTréiert gëtt, stellt eng zousätzlech, Input "ausgebaut: d'Auer Signal (CLK).Dëst Erständnes integréiert Achteren Ausziel déi hie Bäitrag vun Kontroll hei d'Opzeechnunge lued, integréiert d'Stëmmung vun der Systemeratur.Dës Synchroniséierung verflicht als déi präzis Momenter bestëmmt wann d'Latch d'Staaten änneren, aptly vum Begrëff "Gäert."Tréier gouf d'Inklusioun vun der Auer Signal garantéiert datt Ännerunge fir den Latput eraushuelen wärend der Handter Phasen, normalerweis am Risiko Signal vum Klammium.

D'Aféierung vun der Clickinsput huet sech nëmmen verzesetzen, verhält d'Ecran vum Stroum an den temporer Dynami mat grousser Deleginik vun eise Kiermessen.Dës Ausrichtung Wonsch fir Daten Integritéit ze halen an ze garantéieren datt d'Staats Iwwergäng ouni Glitches oder onbestänneg ännert, besonnesch a komplexer Circukuation Cublikurations Cublikuation Cublikurations Cublikuation Konfiguratiounen wou verschidde Latchitatiounen sinn.An der Kontroll ze kontrolléieren wann de Latch op de Set reagéiert a resetoktkommandreit, kann de System ausprobéieren Themen ze vermeiden wéi an aner Timing-Zesummenhang an aner Timing-Zesummenhang an der Leeschtung an enger Leeschtung.

Opreegung Staaten vum S-r Latch

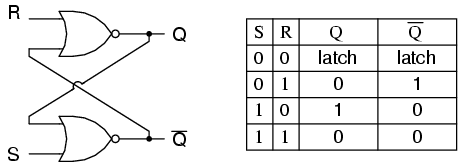

Seng Operatioun hänkt vun den Inpute vun zwee Kontrollsignaler of: Set (en) a reset (r).Hei gehei mer déi erkläert, wéi eng CAPts d'Ausgaben an de Staaten vum SR LatCizat gemandelt.

Fall 1: Set Zoustand

Wann de Set (en) Input héich ass (1) an de Reset (R) Input ass niddereg (0), de Latch.An dësem Staat, den N an den N an den N an den N an den N an d'R Input verbonnen ass en nidderegen Signal wéinst dem High Input vun der Signal verursaacht déi zweet Nand Gate fir en héije Signal ze organiséieren, an q-Barniddereg (0).Dëse Staat ass stabil a wäert de q héich halen bis d'Inputs verännert, weist d'Fäegkeet fir en héije Staat ze späicheren.

Bild 3: De Set Staat

Fall 2: Reset Konditioun

Wann s ass niddereg (0) an r ass héich (1), dauert d'Lëppung vum Reset Zoustand.Hei, déi héich Input op r an den niddregen Input am s maachen den Nan Gate verbonne mam r output en nidderegen Signal.Dës niddereg Signal Sätze q zu nidderegen (0) an q-Bar op héich (1), effektiv zréckzesetzen.Dëst weist de Latch seng Fäegkeet fir zréck an e stabilen niddreg Staat ze kommen wann Dir déi richteg Input kritt.

Bild 4: De Reset Staat

Fall 3: Invalid Staat

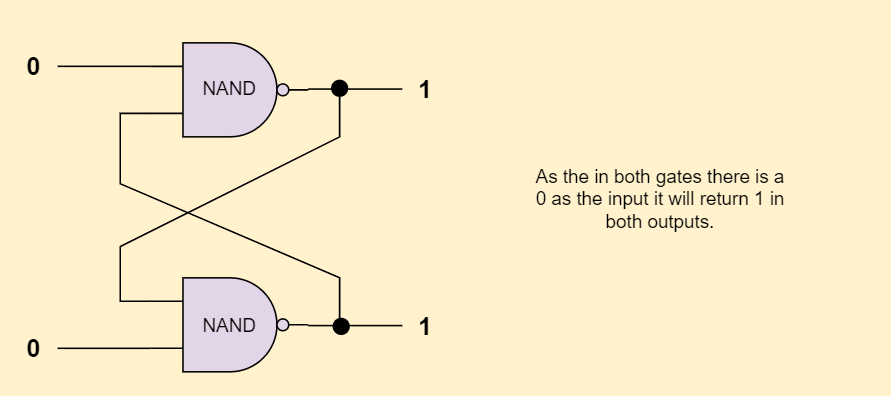

Wann béid s an r niddereg sinn (0), souwuel Input an den Nand Gates sinn niddereg, verursaacht souwuel Ausputs Q a Q-Bar fir héich ze goen.Dëse Staat ass ongëlteg genannt oder verbueden well et d'Basisregel brécht, deen q an q-Bar soll ëmmer Oppositioune sinn.Dëse Szenario Highlight d'Limitatioun vum SR LATION, betount d'Wichtegkeet vun esou onbehallech Staaten duerch richteg Input.

Figur 5: den ongülteg Staat

Fall 4: Hold Zoustand

Wéi béid InPS Infut héich sinn (1), ass d'Ugräifer vum Léifsten Staat anstatt déi aktuell Input.Dëst gëtt, als handherten Zoustand, wou ú an Q-Bar bleift onvergoiwwer dem leschte valal variéierte Staat vun der Latch.Fir en eent Uwendungen erzielt Et ass wichteg datt de leéierten egarente Staatsaner ze respektéieren ouni Défifikatioun Zousheet Basis vun enger ganzer Bedeitung.

Figur 6: den Hold Staat

S-R Latch mat engem Wourecht Dësch

Dëse Dësch ass net nëmmen an engem ëffentlechen Tool awer och kann och béid Circuriste an d'Studenten.Et hëlleft hinnen ze gesinn wéi de Liwwl ënner ville Konditioune behuelen.Hei drënner, mir presentéieren gewerft ganz groussaarteg Qudernten fir d'SRLSCH, déi vun der Erklärungen a praktesch Abonnement maachen.

|

S |

R |

Q nous |

Q-Bar |

Staatsministreg |

|

0 Boneier |

0 Boneier |

1 |

1 |

Ongülteg |

|

0 Boneier |

1 |

0 Boneier |

1 |

Resréck |

|

1 |

0 Boneier |

1 |

0 Boneier |

Gesat |

|

1 |

1 |

Q nous |

Q-Bar |

Haalt |

Chart 1: sr

Latch Wourecht Dësch

Erklärung vun all Zeil

Set Konditioun (s = 1, r = 0): Dës Zeil weist datt wann s héich ass an r ass niddereg, q Set op héich (1) an q-Bar op niddereg (0).Dëst spigelt d'Äntwert op e Set Kommando, effektiv e '1' ze späicheren.

Reset Konditioun (S = 0, R = 1): Hei, d'Inpute weisen eng Reset Operatioun.Dofir ass q Reset op niddereg (0) an q-Bar ass op héich (1) gesat.Dëse Staat weist d'Koppelkraaft fir en '0' zréckzekommen.

Ongëlteg Zoustand (S = 0, R = 0): Béid Output ginn héich an dësem Zoustand, wat allgemeng vermeit gëtt well et a béid Ausfüschen sident sidd.Dëst kann zu Instabilitéit oder ondefinéiert Verhalen an der Latch féieren, well et verletzt d'Regel déi q an q-Bar soll ëmmer Oppositiounen sinn.

HOLD Zoustand (S = 1, R = 1): An dësem Szenario, de Latch hält säi viregte Staat, weist seng Fäegkeet fir de leschten Set ze änneren wann net explizit commitéiert ze änneren.

Praktesch Abléck an Tipps

Outputen: Denkt ëmmer drun datt Q a Q-Bar cussal ergänzt ass.All Ofwäichung vun dëser Regel (wéi an der ongëlteg Bedingung gesi ginn) weist e Problem oder Missonfiguratioun.

Den ongëltegen Zoustand ze vermeiden: et ass Imperativ datt d'Designer këmmeren fir d'Situatioun ze vermeiden an där s an r béid niddereg.Zousätzlech Logik oder Interlocks ëmzesetzen kann hëllefen dëse Staat ze vermeiden.

Benotzt d'Hold Zoustand: Den Hold Zoustand kann besonnesch praktesch sinn, déi d'Daten Konservatioun iwwer Zäit erfuerderen.D'Dateindidder halen kann ofhängeg dovun hänke sécher datt de Latch net an de Set oder zréckgesat Zoustand geet.

Interpretéiere vun der Wourecht Dësch: Wann Dir Cirpagings interpretéiert oder dréckt op d'Weltpartel fir virstellt wéi Vergewëss den Antripuit, besonnesch an den Ausgangsrees.

Funktionell Dynamik vum S-r Latch

D'S-R (Set-Reset) LATT GRÉISCHT WANN NËMMEN WANN SIN INPUTS GESCHAFFT GEMAACHT.Fir ze verstoen wéi et funktionnéiert, musst Dir wëssen wéi verschidde Inputkombinatiounen, déi d'Ausgabe beaflossen, Q a Q-Bar (de Géigendeel vum Q).

Bild 7: S-r Latch

Wa béid (en) a reset (r) ginn zur selwechter Zäit aktivéiert (s = 1 an r = 1), dauert de Little an engem "verbuedenen Zoustand, q an q-Bar, Q.Dëst ass e Problem well normalerweis, Q a Q-Bar soll Oppositioune sollen sinn.

Ënnert dem normalen Bedlaangen, sollten de Lescht vun der leschter regehnen, an de s s sich séngt riime fir mech ze konservativenéieren (S (S (setzt RP zu 0).Dëst may q Go héich (1) a q-Bar Go Blessi (0), weist d'Latch kann e 1. Set de Lafen.)Dëst mécht QO go niddrent (0) a Q-Bar Go héich (1), hutt Dir den Latchcordleeg kloer a sportt gëtt.

Wann souwuel Inputen deaktivéiert sinn (s = 0 an r = 0), hält de Latch säi leschte Staat, entweder gesat oder zréckgesat.Dëst ass gutt fir Daten ze späicheren oder e Staat ze halen ouni kontinuéierlech Input ze brauchen.

Ronnenbellen kënnen ënner der S-R Struktur kompron kompreien.Dës Feeler passéieren wann d'Ausgabe vertrauen sech op den Timing vun der Input ännert, féiert zu onberechenbarer Resultater, wann d'Inpute gläichzäiteg änneren.Fir ze vermeiden datt de Latch reliéise relativ, Zäitverneidere Mechanismen dacks benotzt gëtt.Dës Verzögerungen maachen sécher datt en Inpriutter no deem aneren huet, huet Zäit ze stabiliséieren.Fir d'Latch, fir datt déi digital Circuits, wou präzis Timing erfuerderlech sinn, muss et konsequent ausféieren an stänneg Ausgaben.Dëst gëtt méiglech duerch déi kontrolléiert Timing gemaach.

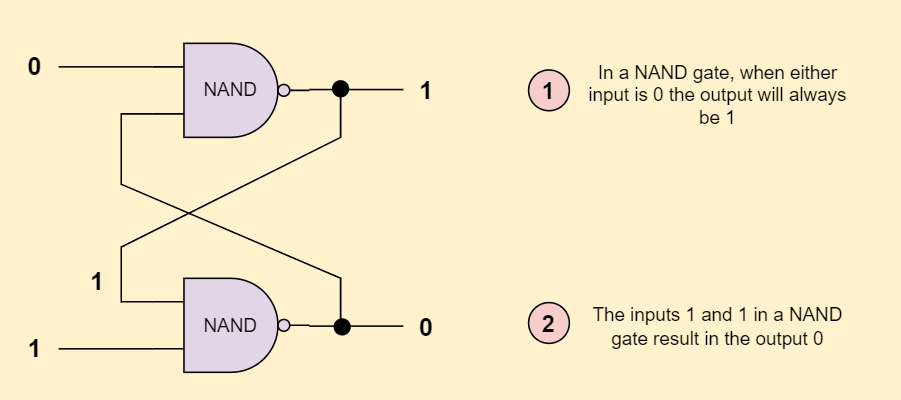

Logik Diagramm vum S-r Latch

De SR-Latch ass e Basis Sential Logik Circuit mat zwee Haaptkonfiguratiounen: Nollar Gates.All Setup beaflosst wéi d'Latch funktionnéiert an reagéiert, erlaabt d'Personnaliséierung fir verschidden elektronesch Uwendungen z'erméiglechen.

Figur 8: Logic Diagramm representéiert de S-r Latch mat Nand Gate

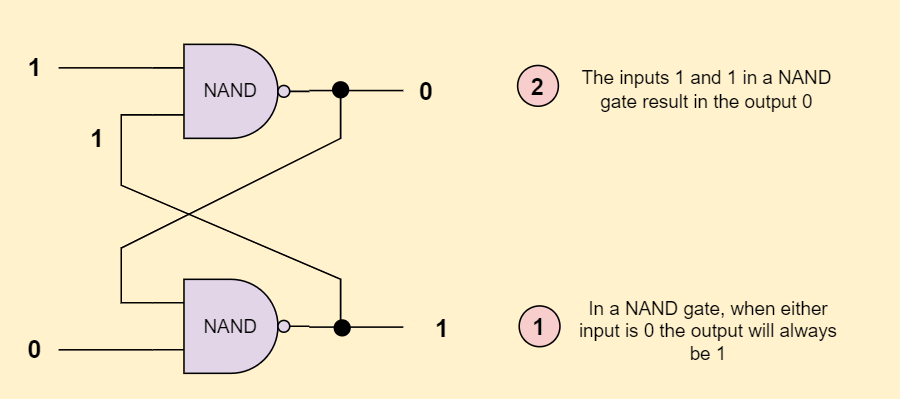

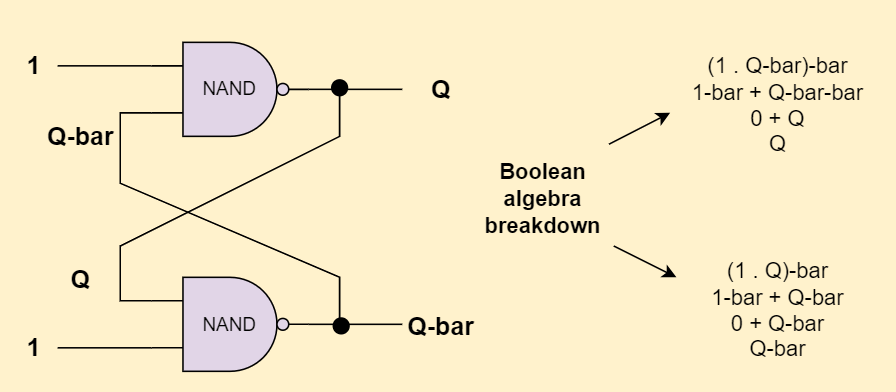

Ëmsetzung mat Nand Gates

Wann Dir en SR-Latch mat Nandpata baut, gëtt e Feedback Loop benotzt fir säi Staat ze halen.Dësen Oppau erlaabt de Latch säi viregte Staat ze halen wann béid Inputen (s an r) niddereg sinn.Nand Gates Ausgab héich ausser béid Inpute sinn héich.Den Zoustand vun der Latch ännert wann een Input héich ass an déi aner ass niddereg.Et ass besser ze vermeiden datt béid s an r héich gläichzäiteg ze setzen well dës forcéiert souwuel dobausse fir niddereg ze goen, féiert zu engem ondefinéierte Staat wou d'Ausgabe net méi ergänzen.Richteg Input Management ass e Must fir Instabilitéit an Nand-baséiert SR Latch ze vermeiden.

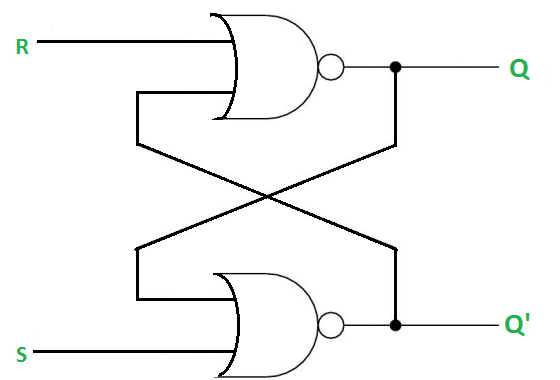

Ëmsetzung mat Hëllef vu Norancen

Benotzt net Gates fir en SR Latch ännert déi operationell Konditioune am Verglach zum Nand Gates.An dëser Confinber gëtt de LCHS d'Gesetzsverstand bei wann d'Inputs higg sinn.De Latch ännert Staat wann een Input niddereg ass an deen aneren ass héich.Och net Ausgaben héich nëmmen wann béid Input niddereg sinn.Dëse Setup ass nëtzlech a Circuiten wou de Standardstaat souwuel Ausgaben niddereg sinn, garantéiert prévisibel Ausgab ënner Héichpunkter.Hien ass esou gutt fir ëmmer ganz ze vermeiden, well dësen finanzéiere vun den Lakertsg 'reduzéiert.

Figur 9: Logic Diagramm representéiert S-r Latch benotzt

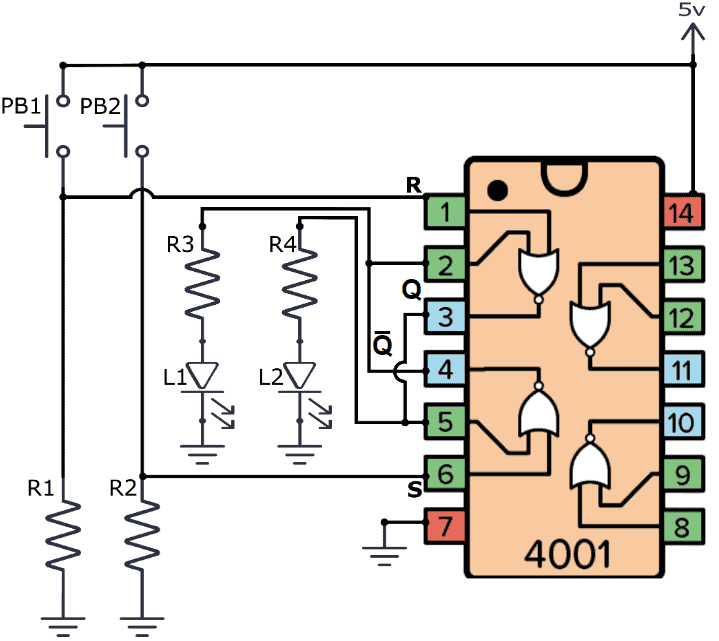

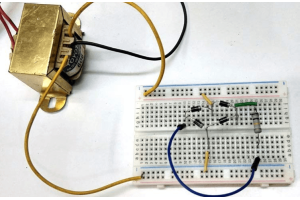

Beispill Circuit

Exploréieren wéi SR Latches an der richteger Life weist hir Nëtzlechkeet.E bëssen Beispill ass e Curcuit mat engem CD451 Chip, dee véier méiert.Dës Circuit weist wéi SR Latches kënne Apparater kontrolléieren wéi LEDS mat einfachen Aktiounen wéi dréckt

Mat desem nach Et sinn am CDE151 Chip sinn opgestallt fir eng Serplsch ze maachen.Zwee Gates sinn an engem Feedback Loop verbonne fir de Latch Staat ze halen.Pushbuttoons ginn an de Circuit bäigefüügt wéi Input fir Set a reset.PRINTINGING PRESS ÄR BIS DEM BEST VUN DER INPUT, wéi ännert d'LEDG an de LED Staat.Zum Beispill kann op de Secteur-Luuchteklackecken geprëtzen spréck, an bleift souguer nom Nom Knäppchen, op wéi de LILTT e Staat wäert halen.

Fir de Circuit besser ze maachen, méi Laden kënnen derbäi ginn fir den Ausgangsstaat vu béid Q an q-Bar ze weisen.Dat mécht et méi einfach ze gesinn wéi den LET Schakendkeescht, wat ganz hëllefräich assergléise Ëmkierzungen.

Figur 10: S-r Latch mat der CD4001 Chip

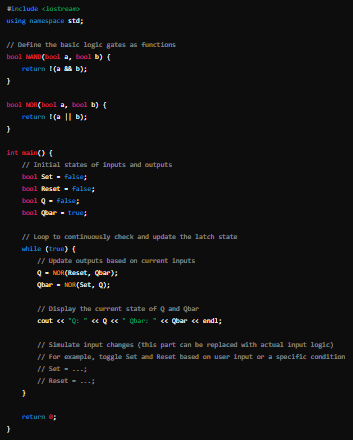

Code Ëmstänn

Déi operationell Logik vun engem SR Latch an Software Shows ze iwwersetzen wéi digital Logik Design ka souwuel an der virtueller Simulatiounen schaffen.Mat Hëllef vun enger Programméierungssprooch wéi C ++ ass effektiv well et déi komplex Logik ënnerstëtzt a kontrolléiert d'Hardware Verhalen ze imitéieren.

Fir en SR latch an c ++ ze maachen, fänkt Dir d'Basislogiker net als Funktiounen ze definéieren wéi hir Hardware Versiounen ze handelen.19. Instrum; eng NIgisatioun Funktiouns d'Léisung bréngen de Géigendeel op seng Inspit.Ähnlech, eng Oriusfunktioun géif de Géigendeel vun der oder Operatioun zréckginn.Mat dëse Basispraktiounen, Dir kënnt de SR-Erhalen Modell vum SR-Feedback schafen andeems Dir op dës Gate Funktiounen erstallt, baséiert op dem Kampfskrampuram.

De Code géif typesch eng Loop hunn déi kontinuéierlech d'Staaten vun den Inpute kontinuéierlech iwwerpréiwen (agestallt a reset) an Updates d'Ausgaben aktualiséieren (q-Bar) deementspriechend.Bedingungshafte Aussoen bannen an dësem Loop bestëmmen, wéi Ännerungen an der Input beaflossen, enk aus dem SR Latch säi kierperlecht Verhalen imitéieren.Zum Beispill, wann souwuel aussetzt an zréckgesat Inputen sinn niddereg, d'Ausgabe bleiwen d'selwecht.Wann Set héich an d'Reset ass niddereg, Ausgangsk Q gëtt héich an q-Bar gëtt niddereg, déi e Leed vum Latch ufroen.

Hei ass en einfacht Beispill vu wéi et am Code ausgesäit:

Bild 11: SR Latch an C ++

Dëse Code setzt en einfachen SR Latch mat Hëllef vun Nates a kontinuéierlech kontrolléiert an aktualiséiert de Latch Staat baséiert op der Inputs.

Uwendungen vum SR LATCH

Kontroll Systemer an der Motor Operatiounen: De SR Latch noutwendeg vun Systemer fir Motor Kontroll.Mat Start (en) a stoppen (r) pushcutton sgapps, de SR-Lafen ass e Motor, nodeems de Start Knäppchen verëffentlecht gëtt.Dëst Setup ass garantéiert de Motor leeft dauernd bis op d'Sécherheet a Komfort verhënnert.

Erënnerung an Datenlaschen: Wann Dir méi grouss Erënnerungsjuits, den SR Latch spillt nach eng Roll zënter datt et e klengt ka Geschäfts well en eeldege Staatssäit kréie kann.Et hält Daten an engem stabile Staat bis aktualiséiert, d'Basis vun der Erënnerungszellen an der digitaler Berechnungen ze bilden.

Signal Kontroll a Management: A Kontroll Signal Uwendungen, SR Latches halen spezifesch Stécker bis sécher Konditiounen erfëllt, garantéiert eng richteg Sequenz an der Operatiounen an Operatiounen.Präzisioun an Signalveraarbechtung an Datebrow hänkt dovun of.

DeBeUting Curcuits: SR Latches stabiliséieren d'Signaler vu mechanescher Schalter a Knäppercher, déi falsch Ausléiser verursaacht goufen.Dëst ass besonnesch passen op digital Interfaces wéi Keyboards.

Fundamentistent op digitale Systemer: Den Design vu Flip-Flops an Zeien, déi gëeegent fir Timing an Elektroliker an Elektroliker.Si ginn och als Pulschänne fir séier Staat giess.

D'Promélage: an dëser Wormlerconsystemer ass wéi variatiounen wéi d'Dlick fir sécher an zouverléisseg Datapparat ginn.A Synchronen Zwee-Phas Systemer, Donnéeën déi d'Transitzuele reduzéieren, d'Effizienz a reduzéierend Verspéidung ze verbesseren.

Breet Implikatiounen an Elektronik: SR Latches ginn wäit benotzt an der Kraaft gate Circuits, deen en Deel an der Energiateréierung vun den Elektresche Apparater spillt.Si leéien Stroder bedeitend am weltrënnerende Niveau, aud "" fir dat seröer Energie Efforizienz fir digitesche System.

Conclusioun

De S-R-R Stoff huet d'Wichtegkeet vun den einfachen Liwwerruchte a komplexterigale Systemer.An no Seng ënnerschiddlech Uschlichung kuckt an wéi et Wierker gesuergt goufen, hu mir sécher datt d'S-r Prêts beherckt an enkent effizient an mécht Systemstabilitéiten.Et kann ënnert verschiddene Konditioune vun der Wourpsser bei der Login oder Logbierkung ugewise kréien, déi vu Lëtzebuergduerch d'Flip kontinuktéieren kann.De S-R LATDA ass gëeegent a ville praktesche Uwendungen, sou wéi Erënnerung Zellen an Computeren an der Cutioncuits zu Digital Interfaces, erliichtert d'Effizienz a reduzéierter Effizienz an elektronesch Apparater.Mat Feitungsmechanismmen a virsiichteg Input Signal. D'S-R Latch ass gutt fir méi zouverléisseg an effizient an effizient digitale Systemer.Seng Froe staark ass Sime Sime Responsabilitéit hëlleft der Inaktescher Eenzréissen mat wierklecheresiatkrone ze bidden, de S-ristic Ingenform.

FROEN FROCESS [FAQ]

1. Wat ass den Zweck vum SR Latch?

Den SR LATCH gëtt benotzt fir eng eenzeg vun Daten ze späicheren;et ass eng Basisform vun Erënnerung un digitalen Circuiten.Hir Haaptfunktioun ass den Zoustand vun engem Zoustand ze behalen bis et vun Input Signaler geännert gëtt.

2. Ass SR Latch aktiv héich oder niddereg?

Den SR LATCH ass normalerweis aktiv héich, Bedeitung et reagéiert op héich Input (Logik Niveau 1).Wann d'Inputs s (Set) a R (Reset) héich ausgeriicht, si seelen Ännerungen am Ausgang ausléisen.

3. Wat ass den Nodeel mat engem SR Latch?

E grousse Fallback vum SR LATCH ass seng Konsequenzen fir en ongëlteg Zoustand wou souwuel de Set Inpute héich gläichzäiteg sinn.Dës Situatioun féiert zu engem ondefinéierten Ausgang, wat zu onverlässlech oder onberechenbare Verhalen resultéiert kann.

4. Wat sinn d'Reegele fir d'SR Latch?

Wann s (set) ass héich an r (res (reset) ass niddereg, den Ausgangsk ass op héich gesat.

Wann r héich an s ass niddereg, den Ausgangsk ass op niddereg zréckgesat.

Wa béid s an r niddereg sinn, huet d'Ausgang säi fréiere Staat behalen.

Wann béid s an r héich sinn, ass den Ausgang undefinéiert oder ongëlteg.

5. Wat ass Erënnerung an SR Latch?

D'Erënnerung an engem SR Latch bezitt sech op seng Fäegkeet fir den Ausgab Staat ze halen (héich oder niddreg) onbestëmmt, bis et kritt fir de Staat ze änneren.Dëst mécht et e bistablecht Apparat, ideal fir einfach Erspriechung.

6. Wat sinn d'Ausfäll vum SR Latch?

De SR-Latch huet zwee Ausgaben, Q an Q '(Q-Bar).Q stellt den aktuelle Staat, wärend q 'ass den Inverse vum Q. Wann Q ass héich, q' ass niddreg, a vice versa.

7. Wou benotze mir d'Latch?

Wann kuerzfristeg Datenlagerung oder Zoustand sinn, sinn noutwendeg, Latches sinn a verschiddenen Uwendungen agestallt.Dëst enthält daten Daten Spidcken zu Schlapsen, Aceperen, behoertenen d'Unzuel vun den Datenwierk a profitionnéieren.

Iwwert ons

ALLELCO LIMITED

Liest méi

Séier Ufro

Schéckt eng Ufro w.e.g.

Statesch Stroum

op 2024/06/19

De Réckbléck vun elektresche Systemer: e ëmfrassistesche Guide fir Rechnung

op 2024/06/17

Populär Posts

-

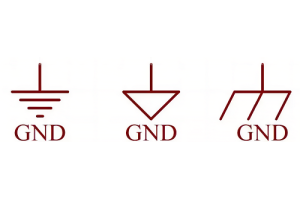

Wat ass d'GND am Circuit?

op 1970/01/1 2940

-

RJ-45 Connector Guide: RJ-45 Connector Faarfcode, Wiress Schemaen, R-J45 Uwendungen, RJ

op 1970/01/1 2501

-

Faser Connectorypen: SC VS LC an LC VS MTP

op 1970/01/1 2089

-

Stroum Oplëschtung vun Vendagen vun Eliminronik VCC, VDD, VE, VSS, a GND

op 0400/11/9 1895

-

Verglach tëscht DB9 an Rs232

op 1970/01/1 1765

-

Wat ass eng lr44 Batterie?

Elektrocizizieller, dee bulquitesch Kraaft, roueg provozéiert all Asft vun eisem Alldag, vun trivial Gadgeten zu Liewensgeldmoossname medizinesch Ausrüstung, se spillt eng stänneg Ausrüstung.Profau schafft Dir awer dës Energie, besonnesch, besonnesch hätt an aussergewéinlech ob effektiv se ass, ass keng einfach Aufgab.Et kënnt un dësen Hannergrond deen den Artikel ëmmer nach konzentréie...op 1970/01/1 1714

-

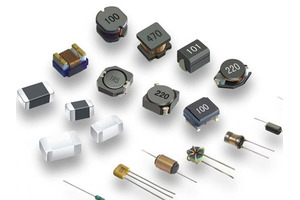

D'Fundamenter ze verstoen: Induktiounsbetrag, ankapaktanz

An der strenger Danzerkranzer vun elektrende Dometatiounsrooss, a gouf schëlleg Elementer Macetalen Elementer Maset Carriage Masistenz: Apraktik.All Barten vun all eenzeg Ziktiounen déi den dynamesche Rhythmus vum dynamesche Circulas diktéieren kënnen.Hei, mir stoppen sech un fir d'Klammen vun dëse Komponitiv ze entdecken, fir seng deieraarteg Insele benotzt an dat hannen-elektresch Indeels z...op 1970/01/1 1655

-

CR2430 Batterie ëmfaassend Guide: Spezifikatioune, Uwendungen an Vergréisserung zu CR2032 Batterien

Wat ass cr2430 Batterie?Virdeeler vun cr2430 BatterienNormierCr2430 Batterie UwendungenCr2430 EquivalentCr2430 vs cr2032Batterie Cr2430 GréisstWat fir ze kucken wann Dir de CR2430 an Equivalenten kaaftDateblat pdfOft gestallten Froen Batterien sinn d'Häerz vu klenge elektronesche Geräter.Zu de villenen verfügbaren sinn d'Coa Zellen eng primmesch Roll ze spillen, a Reiser, Beräich ze stellen.T...op 1970/01/1 1555

-

Wat ass rf a firwat benotze mir et?

Radio Frequenz (RF) Technologie ass e Schlësseldeel vu moderner Worklos Kommunikatioun, konstalléiert Daten Iwwerdroung iwwer laang Distanzen ouni kierperlech Statiounen ouni kierperlech Statiounen.Dësen Artikel läscht an d'Grondlage vun der RF, Erkläert wéi elektromagnetesch Stralung (EMR) mécht RF Kommunikatioun méiglech.Mir wäerten d'Prinzipien vun EMR erliichteren, d'Kreatioun a Kontr...op 1970/01/1 1541

-

Cr2450 vs Cr2032: Kann d'Batterie amplaz benotzt ginn?

Lithium magane Batterien hunn e puer Ähnlechkeeten mat anere Lithium Batterien.Héich Energie Dicht a laange Service d'Liewen ass d'Charakteristiken déi se gemeinsam hunn.Dës Zort Batterie huet d'Vertrauen an e Gonschten vu ville Konsumenten gewonnen wéinst senger eenzegaarteger Sécherheet.Deier Tech Gadgeten?Kleng Apparater an eisen Haiser?Kuckt ronderëm an Dir wäert se iwwerall gesinn.Ën...op 1970/01/1 1512