op 2024/05/10

604

Detailléiert Guide fir voll Adder

Am Recht op digital Elektronik a Computerénger, déi eent vun deem déi meescht wiesentlechst Béirochen, pivomesch Crimpf.Als implizal Komponenten vun der aritescher Logik Eenheet (Alu), Adder, an d'Agener Operatiounen erliichteren, rangéiert vun der Basis Archical fir eng komplex Opreegung fir komplex Operatiounen.Hieschen Design, wat sech vun einfacher Helde qurodscht bis méi komplex Adeles vun méi Veraarbechtung vun der Veraarbechtung sech aus den Zéisen vun der Veraarbechtung sech aus den Zéierfaltiker attianen.Dës Date vun der WEIDER an déi dialderlech Kontext am draaleschen Logicost vun Adelical Design.

Calalog

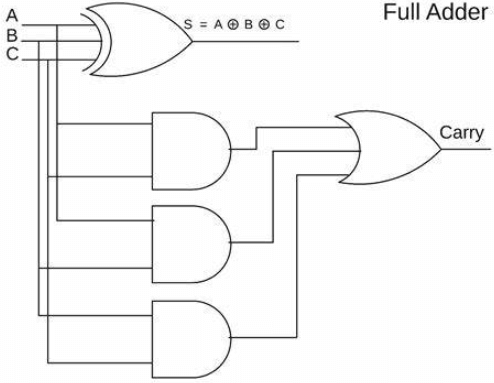

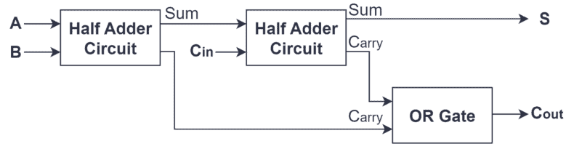

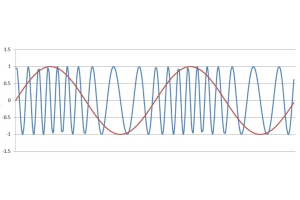

Figur 1: Voll Häder

E Ersatz ass e fundamentärecaluville Concours a elektronesch Engistronom a Spillt eng zentral Roll a méi komplexer Kompetenzen.Als Deel vun der aritescher Logik Eenheet (ALU), d'Verhältnisser eng Vielfalt vu wesentleche Computeren.D'Effizienz a Performance vum ganze Prozessor gëtt direkt vum Design an der Funktionalitéit vum Adder beaflosst.

Am Prozessor gëtt den Adder net nëmmen fir Basis Arithmetik Operatiounen a Wunnsuchung an Äerdbetrichtung benotzt, awer et ass och engagéiert sech och op engem breere Beräich vun logeschen Operatiounen.Zum Beispill, kaaft wann de Prozessor dacks leeft, muss nei Ersëtzungen ze hunn.Dëst gëtt normalerweis gemaach andeems se vun der aktueller Adress vun der Aufgab derbäigesat oder subtrahéiert sinn.Si kontrolléieren d'Zuel vun de Loop Iteratiounen an de Gesamtfloss duerch Erhéijung vun Erhéijung vun Zauberer.A méi komplexer Uwendungen, sou wéi Table Indexéierung, Adderen séier Donnéeën andeems se Offsetzunge berechnen.Dat fir ass wichteg Datementogungsystemiase wichteg, a grousse Skyvalaktivéiere Veraarbechtung.Ahener sinn och Schlëssel an enger gewësse Loftstechniken a Multi Niveau Cacheme betreffen, firzefroen dann op Donnéeën ze bestellen, Effizienz bericht ze bestëmmen, d'Aktiounsauuer, d'selwecht. D'Donnéeën ze bestëmmen wäert d'Donnéeën Offizienz profitéieren.

Technologesch, Anhen ginn Anhust duerch verschidde Crecucs abegraff, da parallel, Meiglech, a Pipeline Adder.Parallel Addere gi fir hir Fäegkeet favoriséiert fir verschidde Zifferen gläichzäiteg ze handelen, maache se fir Szenarie fir séier Berechnung ze maachen.Serial Adder, op der anerer Säit, Prozess e bësse pro Clock Zyklus a sinn ideal fir Ressource limitéiert oder niddereg-Kraaft Ëmfeld.Pipeline huet sech zougestallt, Prozess fir déi eemol an e puer Etapp, all Deel vun der Zousätzlech opmaachen.Dësen Design wesentlech boosts Computatiounssituatioun, besonnesch an héich Performance Computéierungsëmfeld.

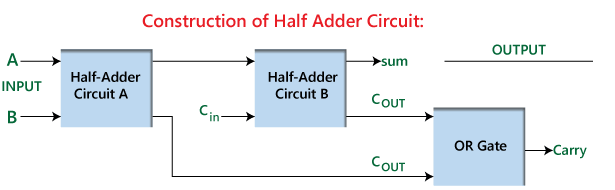

En halleft ADDER Circuit ass e fundamental Gebai Blockéierung vun der Digital Electronics, speziell entwéckelt fir zwee eenzeg Binär Zifferen ze addéieren.Dës Cucula Formen bilden d'Fundament vun engem vollen Adder an ass Schlëssel fir méi komplexe Logik-Tircuit ze verstoen.An der Halschent vum Recht sot et, sinn déi zwee primär Inmfs, e bezeechent an en anbem ass, deem déi Ausdiewen an den adwend deelfënnt.Dëse Setup erméiglecht et fir d'Zomm ze berechnen an d'Ausgaben Output ouni Noutwennung vun der fréierer Berechnung ze maachen.

De Kär vun engem hallwen-Adder besteet aus zwee Logik Gates: en xorpaart an en anDen Xorpaart ass verantwortlech fir den Zomm Ausgab ze generéieren.Et funktionnéiert ënner enger einfacher Regel wou et erausgeet wéi nëmmen eng vun hiren Inputs 1;Soss, et geet en 0. dem an den anen Tornen, op der anerer Säit, verschafft d'Ausgangsstéck.Et produzéiert eng 1 nëmmen wann souwuel seng Input 1 ass, alignéiert perfekt mat de fundamentalen Ufuerderunge vun der Binär Zousatz.

Figur 2: Bau vum halwenhiewen

Dës effizient an direkt Design erlaabt den Halwen Adder net nëmme fir Basis Binär onofhängeg ze maachen, awer och fir als Baublock ze servéieren fir e komplette Block ze schafen fir e komplette Verhënnerung ze kreéieren.E vollen Uerder ass gebaut andeems Dir zwee hallef Hälschungen mat engem zousätzleche oder Gate komesch kombinéiert.An dësem Setup, déi éischt hallend Erhuelung hëlt den initialen Zousaz Aufgab, generéieren eng virleefeg Zomm a droen.Déi zweet Halschent Verhiewe verschafft dann d'Ausdrock vun der éischter laanscht mat engem zousätzlech Ausgang Input.Schlussendlech, d'oder Gate fusionéiert déi zwee droen Ausféierung fir de finalen Trainingsausgang ze produzéieren.Dës Stiermer bestetzt d'Funktionalitéit vum Adder, aktivéiert et ze verschaffen, méi komplex Vëlzungen ze verschaffen, Kalureapplikatioun an d'Generalstruktioun am Digitalialesëtz.

Einfach anzeschreiwen ass e verstuerwenen Transport an der digital Logikatikateschen, equipéiert fir den Zousaz vun dräi eenzeger Bagesch Däiwel ze behandelen, an a wéi eng (Cincouts).Dëse Design erlaabt de komplette Verhaftung fir effizient compriéis Cinäradraim ze beaflossen andeems Dir d'Ausdrock vun de leschte ënneschten Uerdnungsberechnunge an enger eenzeger Operatioun integréiert gëtt.

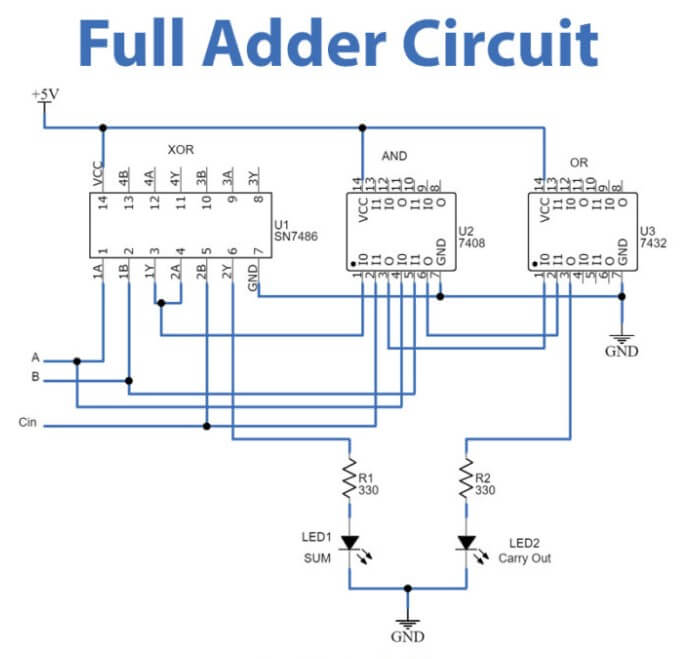

Figur 3: Voll Aklang Circuit

Funktionell, kann e ganzt Adder eng zwou Zuelen austrieden, déi seng Output ass vun 0 bis 3, an et kann och en Ausbezuelen produzéieren (Matbau).Dëst geschitt well, wann all Input Bits op 1 (a = 1, b = 1, Cin =), den Zomm Ausgab assEn zousätzleche Gebai muss op déi nächst méi héich gebraucht ginn.

Strukturell, ass de komplette Adder allgemeng aus zwee hallef Anhänger an engem oder Gate besteet.Déi éischt Hieft demhëllt hir Ariicht an b, generéiert eng initialen Zomm an engem droen Signal.Dës initial Zomm ass dann fidderen, zesumme mam Carric (Cin), an d'zweet Hallo.Déi éischt Feierhuelung vun der Roll ass dës Zomm aus der éischter hallwer Uerder an den Cumm ze bidden, eng aner Zomm ze produzéieren an en neien Ausgang.Gläichzäiteg, den Duerchféierung vum éischten halleft Half an den Duerchduechte Output vun der zweeter Halschent Verloossunge sinn duerch en oder Gate fusionéiert, kulminéierend an der Finale Carder.Den Design vun dëser Struktur garantéiert datt de komplette Veruechtung effektiv d'Verbreedung vun Trëttoiren zousätzlech Operatiounen zousätzlech Operatiounen maachen, mécht et ideal fir Multi-Bit-Bit-Bit Ergänzunge ze maachen.Esou gëtt den Design vun de komplette Studente just net nëmmen d'Digitziefen an d'Archometeritéitsvirschung vun der Arrise iwwerwierklechkeet.).

|

Parameteren

|

Halwer Häder

|

Voll underder

|

|

Broessdatsch

|

Halscht Adder ass eng kombinational Logik

Circuit deen zwee 1-bit Zifferen bäidréit.Den Hallef-Erhale produzéiert eng Zomm vun deenen zwee

inputs.

|

E vollen Häder ass eng kombinational Logik

Circuit déi eng Zousätzlech Operatioun op dräi eenzeg binäre Zuelen mécht.

Dee vollen Häeren produzéiert eng Zomm vun den dräi Inputen an droen Wäert.

|

|

Virdrun Ausdréck

|

De fréiere Fuert gëtt net benotzt.

|

De viregte droen gëtt benotzt.

|

|

Infensen

|

An halwer Adder ginn et zwee Inputbits (a,

B).

|

A vollem Adder, ginn et dräi Input Bits

(A, b, can).

|

|

Outputs

|

De generéierte Ausgang ass vun zwou Stécker-Zomm

an droen aus dem Input vun 2 Stécker.

|

De generéierte Ausgang ass vun zwou Stécker-Zomm

an droen aus dem Input vun 3 Stécker.

|

|

Benotzt

|

En halleft ADDER Circuit kann net benotzt ginn

d'selwecht wéi e Vollodule Circuit.

|

E vollen Ukënnegungskrees kann op der Plaz benotzt ginn

vun engem halwen Uklo Circuit.

|

|

D'Feature

|

Et ass einfach an einfach ëmzesetzen

|

Den Design vun engem vollen Häeren ass net als

einfach wéi en halleft Adder.

|

|

Logesch Ausdrock

|

Logesch Ausdrock fir den halte Verhalen ass:

S = A⊕B;C = a * b.

|

Logesch Ausdrock fir voll Adder ass:

S = A⊕B⊕CIN;C 'ausser= (a * b) + (can* (A⊕B)).

|

|

Logik Gates

|

Et besteet aus engem Ex-oder Gate an een an

Gate.

|

Et besteet aus zwee Ex-oder zwee a Gates,

an een oder Gate.

|

|

Uwendungen

|

Et gëtt a Rechner benotzt, Computeren,

Digital Mesuren Apparater, etc.

|

Et gëtt a multiple Bit Ergänzunge benotzt,

digital Prozessoren, asw.

|

|

Almeschen Numm

|

Et gëtt keen alternativen Numm fir d'Halschent

Adder.

|

E vollen Häder ass och bekannt als Ripple-droen

Adder.

|

CRANANCARL...ar

1: Ënnerscheed tëscht der halwer Erhuelung a vollem Veruechtung

D'Wourecht Dësch vun engem vollen Uerder ass de Schlëssel fir seng operationeller Logik ze verstoen, Detailéiert déi präzis Relatioun tëscht binäre Inputbinatiounen an hir entspriechend Ukënnut.Dësen Dësch huet alleg Pripsprifenter an hir Resultater weisen an hir Resultater hunn et en essentock Am Designstumen ze kréien.Fir déi voll Moder Prozesséiert dräi Stell no: A, B, an e Konzent (Cin), kënnen all dovinnzoossen an aacht reservéieren.

Fir all eenzel vun dësen Kombinatiounen, d'Ausgaben aus dem vollen Adder enthalen eng Zomm (Zomm) an eng Ausféierung (MOUT).D'Zomm ass d'Modulo-2 Zousatz (xor Operatioun) vun den dräi Inputen - a, b, a CIN.Den Ausféierung geschitt wann op d'mannst zwee vun den Inputschrits 1. Dëst reflektéiert déi voll Adder d'Fäegkeet fir d'Ausféierung vun der estequemer Zousätzlech zu der Richtegkeet ze behandelen

Ze illustréieren, betruecht den Input Szenario wou all Inputen 0 (a = 0, b = 0, C-in = 0).D'Ausgab Zomm gëtt 0, an d'Daf wäert och 0 sinn, ugewisen datt et keng zousätzlech Zomm gëtt oder d'Féierung ze managen.Wann nëmmen eng Input Bit 1 ass, sou wéi A = 1, B = 0, C-in = 0, déi Ausgabe gëtt 1 mat engem Droen, déi net méi en Ausdrock ass, déi méi héich sinn.Wann zwee Input Bits 1 sinn, wéi A = 1, b = 1, c-in = 0, den Ausgangsset ass 0 (zënter 1 + 1 am Binulo-2)Eraus ass 1, wat en Daf ugewise gëtt, dee muss op déi nächst méi héich gebraucht ginn.De komplexsten Szenario geschitt wann all dräi Input Bits 1 (a = 1, b = 1, C-in = 1);Den Output Zomm ass 1, an et gëtt e Ausbau vun 1, proposéiere datt d'Liwwerung och nach méi héich Stécker erfuerderlech sinn.

|

A K)

|

Elz

|

C 'an

|

S

|

C 'ausser

|

|

0 Boneier

|

0 Boneier

|

0 Boneier

|

0 Boneier

|

0 Boneier

|

|

0 Boneier

|

0 Boneier

|

1

|

1

|

0 Boneier

|

|

0 Boneier

|

1

|

0 Boneier

|

1

|

0 Boneier

|

|

0 Boneier

|

1

|

1

|

0 Boneier

|

1

|

|

1

|

0 Boneier

|

0 Boneier

|

1

|

0 Boneier

|

|

1

|

0 Boneier

|

1

|

0 Boneier

|

1

|

|

1

|

1

|

0 Boneier

|

0 Boneier

|

1

|

|

1

|

1

|

1

|

1

|

1

|

CHART 2: Voll Haftfahrhaut Dréimoment

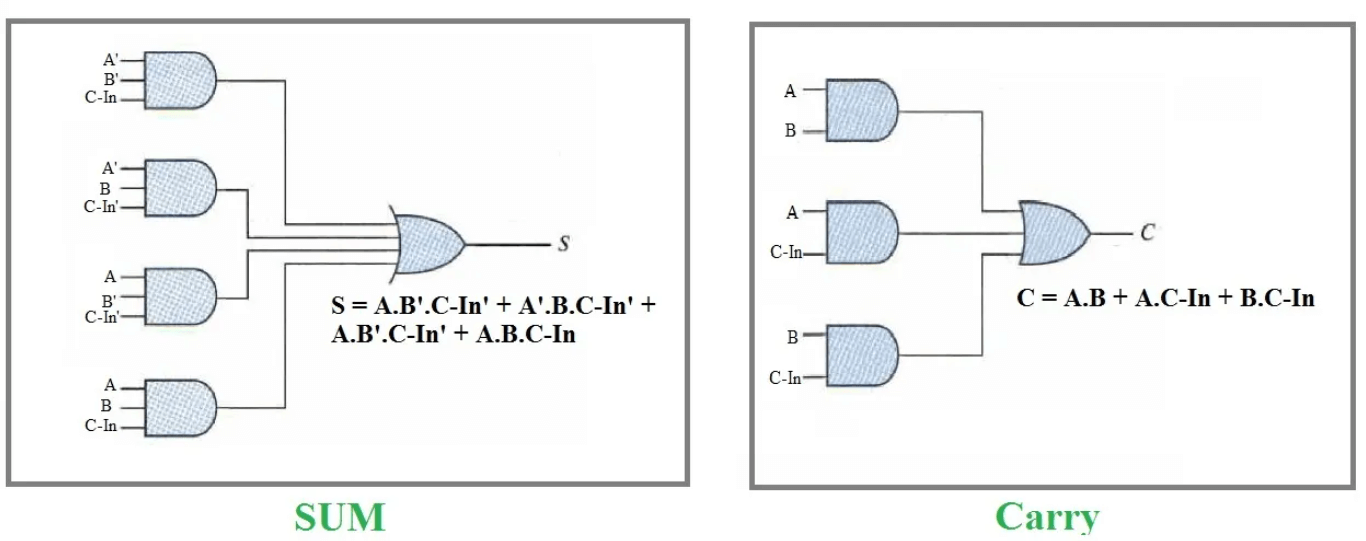

Einfach ze verstoen deen den UDte refuséiert d'Funktionalitéit ze destizéieren mat dem Wourecht Dësch, wou verschidde Kombinatiounen vun Input Wäerter a, an C-In C-In C-in Erputs Zomm.Fir d'Operatioun ze begräifen, mir si vereinfacht d'Logik Equatiounen Schrëtt fir Schrëtt.

Logik Ausdrock fir Zomm

D'Equatioun fänkt mat den ënnerschiddlechen Fäll wou d'Zomm gläich ass 1:

• A 'B' Cin + A 'B Cin' + A B 'Cin' + A. Cin

Dës Equatioun ka konsenséiert gi vum Gruppéierungsagen virgesinn a nom Cin:

• Cin (a 'B' + Ab) + Cin '(A' B + A B ')

Dës Simplifization féiert zu engem méi einfachen Ënnerhalt Form:

• Cin xor (a xor b)

Dës Representatioun weist datt d'Zomm Ausgaben an der xor Operhalt tëscht engem, b, an de Kärbehandlung entsprécht, huet de Kärbehandlung vum binäre Zousaz baséiert op enger komescher Zuel vun enger komescher Zuel.

Logik fir Cut

Fänkt mat Bedéngungen un, wou d'Daf generéiert gëtt:

• A 'B Cin + A B' Cin + ab c-in '+ am Cin

Vereinfachung vun der Equatioun, mir identifizéiere Konditioune, déi allgemeng eng Ausféierung hunn:

• ab + b cin + e Cin

Dir sicht eng wéi eng Form fir de Betrag ze verbréngen, gëtt d'Equatioun erëmbestioune léiere kënnen:

• ab + e Cin + b c-in (a + a ')

Dës erweiderten an nei Erhuelung fir all Szenarie ze erfaassen wou op d'mannst zwee Inpute 1 sinn:

• AB Cin + Ab + A C-in + A 'B Cick

• ab (1 + Cin) + A C-in + A 'B CIN

• AB + A C-In (B + B ') + A' B Cick

• ab + A B 'Cin + A' B CIN

• ab + Cin (a 'B + A B')

Déi lescht kompakt Form fir Cut:

• ab + Cin (a xor b)

Dës Versioun vun der Entféierung D'Equatioun beweist wéi Cute entweder produzéiert wann souwuel A a B 1, oder wann ee vun engem oder B.Pagertéierung a Multikatiounbëssen Binär Zousatz.Dës streamresser Logik ass besonnesch nëtzlech fir effizient digital Circuiten ëmzesetzen.

Figur 4: Equatioune vun engem vollen Unders

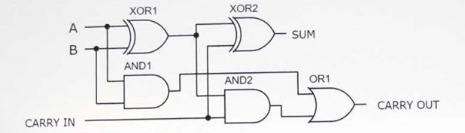

E Promitéiert e vollen Ukënnege Circuit involvéiert suergfälteg eng zwou hallef Animder an en oderDës Arrangement optimiséiert d'Komplexitéit an zielt déi ganz effizient a richteger Beroden.

Fir de Start, déi éischt Halschent hunn d'Verwerter eent primären Binäre Taporte brauch, a b, wat sinn d'Haaptzaufungen dofir ac, wat ass d'Haaptzaufungen derbäigesat.Seng Schlëssel Aufgab ass d'Zomm ze berechnen an den initialen Ausdrock vun dësen zwou Zuelen.Hei, déi éischt Halschent Verloschter liwwert zwee Resultater: eng initial Zomm (Zomm1) an en initialen Ausféierung (droen1).Zomm1 ass ofgeleet vun der Xoroperatioun vun A a B, deen uginn ob den Total eng komesch Zuel vun 1 ass.Fuert1, d'Resultat vun der an Operatioun tëscht A a B, beweist ob béid Zifferen 1, fuerdert eng weider an déi nächst méi héich méi héich.

Nächst, déi zweet Halschent Verhagen huet de Prozess bäi.Et benotzt d'Zomm Ausgab Zum1 an den drëtten Input Cin (duerch eng fréier Berechnung) als Input.Déi zweet Halschent Verhënnerung produzéiert zwee Ausgaben: de finalen Zomm Resultat (Sum2) an de sekundärer Droen (droen2).Sum2, wat ass den Xor Resultat vum Zomme a CAME, representéiert déi definitiv Zomm vun den dräi Input, déi aggregéiert Binär Zousatz weisen.Streck 10, koumen déi vun der Agrëff tëscht Zomm a Cince beassentéiert.

Figur 5: Voll Aklang Circuit mat der Benotzung vun zwou halwer Erhuelung

Schlussendlech, fir de ganzen Adder ze kompletéieren, en oder Gate ass noutwendeg fir d'Ausféierung vun der Fuerer ze behandelenDëst oder Gate ass garantéiert datt all an de Berechnunge generéiert gëtt, ass richteg an de leschte Ausgang.Dofir, dat vollt Finust vum Finderfahrtausgang (Matbau) ass den oder d'Resultat vun der Carrice1 anduerch.The inclusion of this OR gate guarantees that all potential carries are accurately calculated and conveyed to the next level in multi-bit addition operations, ensuring the integrity of the arithmetic operation across multiple bits.

Déi voll analyséieren spille déi onsponsensibel Roll am digitale Login, deen all Wënsch genuch musse berufflechkeeten an verflichtenen Entsementen a verschiddene unzemaachen.Dir eng vu vuxuell Virdeeler och stuerdbar Flexibilitéit Déi schnell Veraarbechtung d'Veraarbechtungsaktiounslicht a effizient Auslooss Gestioun.Dës Spure maachen voll Adäer ideal fir Übung kompümeglech Arritatesch Operatiounen a Logikfunktiounen, besonnesch an Uwendungen, déi d'Hallefmultüme richteg ze maachen.

Virdeeler

Flexibilitéit: Déi voll Adrigder excel aus hirer Fäegkeet fir kleng binär Infinärer Inputen (A, B, Liicht) gläichzäiteg ze verschaffen.Si kënnen och a méi grousse Adder Arrayen erweidert ginn fir méi laang Zuelen ze verschaffen.Dës Skalabilitéit ass wichteg fir héich Performance Arithmetik Logik Eenheeten (ALUS), wat musse komplizéiert Multi-Bit Arithmetik a Logik Operatiounen maachen.

Vitesse: Merci un hir intern Parallel Veraarbechtungsaritecture, voll Adder kënnen d'Zousatz vun allen Input an engem eenzege Clock Zyklus fäerdeg ze maachen, während och d'Ausbezuelen ze bestëmmen.Dës Kapazitéit ënnerstëtzt kontinuéierlech Zousaz Operatiounen an ass onverzichtbar fir Echtzäit Datebank an der moderner Mikrägs an Héichgeschwëllege Computeren.

Nodeeler

Wéi och ëmmer sinn d'voll Akadder och notable Nodeeler.

Komplexitéit an Design an Implementéierung: Voll Händler involvéiert Multiple Tore a Multi-Niveau Dethagung, maacht hiren Design Komplex.Dës Onsauerspréng gëtt net nëmmen d'Häerzuatioun vun den Zushollessimesses ugeholl.

Propagatioun Retard Themen: droen Propagatioun kann duerch e puer Logikpatten passéieren, déi all Retard derbäigesat ginn.Dat kann de ganze Kompetenzag ouni d'Verbesserung während groussen-Skala operatiounen erliechns, besëtzen zesummen an engem entspriechende Compellegkeetsënschtegéiert an héichwäerteg Integratioun.D'Verspéidung kann e wesentleche Flaschen an der Leeschtung ginn.

Fir dës Themen ze reduzéieren, Ingenieuren kontinuéierlech exploitéieren iwwer méi effizient Circuit Designen.Strategien enthalen mat méi séier Logikpaart Technologien, optimuitizéierbare Circuiten fir ze verkierzen Wee Längt, an entwéckelgeschratt Technologien, wéi och Dingologien ze minimiséieren.

Voll Intellitéit sinn extensiv an der digital Logik benotzt, reagéiere fir hir Flexibilien an Effizienz, déi se zentrale sinn an d'Datenveraarbechtung vun der Uwendungen an Datenveraarbechtungen.Hir Applikatiounspann vun der Basis Arithmetesche Operatiounen zu komplex Signalveraarbechtung a System Kontroll.Hei ass en detailléierte Looken op e puer Schlësselberäicher wou voll Adder integral sinn.

Arithmetesch Circuiten

Ee vun de gerechtste benotzte Gebrauch vu voller Verhältnisser ass zu Arithmetesche Circuiten wou se binär Zousatz maachen.Besonnesch entscheedend an Multi-Bit Nummer Zousatz, voll Uerderen net laang Binär Sequenzen duerch Caskading.An dësem Arrangement huet all voll Adder d'Zousatz fir seng Bit Positioun an d'Droen vun den ënneschte Bit, dréckt dann den neien Droen un déi nächst méi héije méi héije méi héije méi héije méi héije méi héije méi héije Bit.Dës Cascade erméiglecht Iech ëmfaassend Multi-Bit Zousatz iwwer déi ganz Gamme vun Zifferen.

Datéierter Veraarbechtung

Déi voll Ariichung spillt och eng Pivothals Roll am chortal Datebank Ocenureg Ocenureg wéi Digital Signalveraarbechtung (Drehomstikatiker a Fönddiktiken.Zousätzlech, am Räich vun der Informatiounsécherheet, inklusiv Datenverrécklung a Feelermetratioun a Korrektioun Algorithmen wéi Paritéitspaktéiert a Cycling Redlatiounspreinung (CRCLACTIALUIZE fir ignoréieren

Router

D'Limas zéien geziftt Aliener sinn déi voll Integratioun ausléisen, fir ganz Inhalungspro-t Funktiounen ze bunktionnéieren, besonnesch a maturparen a Synchronomen.Si bilden eng korrekt ze managen a léinen fir präzis Zielen ze garantéieren.

Multiplexer (Mux) an Demultiplexer (Damux)

A Multiplexer an Ziftiplexer, voll Adelen spille eng kritesch Roll a Kanalauswiesselung an Daten Verdeelung.Si hunn un der Logik deelgeholl déi bestëmmt wéi eng Kanäl fir Dateninput an Output benotzt ginn, Verfeinung baséiert op der Logikverkitalsignaler.

Memory Technologie

An der Erënnerungsadressung, voll Anhänger hëllefen Adressignaler fir dynamesch Zougangsplazen ze generéieren.Dëst ass besonnesch wichteg an dynamesch zoufälleg Zougang Erënnerung (dram) an aner Späicherpersonal, wou voll Adminser-Zousatz fir d'Effizienz vun der Effizienz vun der Effizienz.

Arithmetesch Logik Eenheeten (Alu)

Schlussendlech, sou wéi fundamental Komponenten vun der Arithmetiker Unitéiten an Mikroprocessors an digital Signor Prozessoren, voll Adricial.Den alu handhaben all arithmetesch a logesch Operatiounen, mat vollen Addderen, déi d'Donnéeën déi béid schnell a präzis verschafft ginn.

Voll Akadder ginn mat verschidden Logikercher an Konfiguratiounen gebaut ginn.Hei entdeckt mir véier Proméatiounen, déi sech zoustänneg sinn, da Minigel auszeschalten an oper Umeldung Nuatioune.

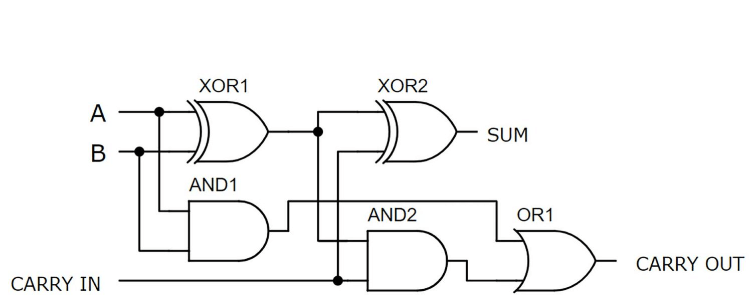

Vollem Verhafter gebaut mat xor, an, an oder Staten

Figur 6: vollem Verhafte gebaut mat Xor, an oder logesch Gates

Dëst Beispill weist e komplette Mënsch, deen op engem Broutbau gebaut huet, andeems Dir d'Iwwerweisungen gebaut hutt.D'Confinuatioun hat fënnef logeschappot: zwee Xap Gate, déi zwou a Gala fäerdeg, an een bezeechnen an engem oderget op insgesant vun 21 Iwwerpositioune z'imakteriséierenInput A a B ginn un der Uewen op der Uewen lénks verbonnen, kritt eng + 5v Versuergung.Dës Inpute gi kontrolléiert mat zwee toggle wiesselt.Zwee LEDs uewen op der lénkser Säit weisen d'Staaten vun Input A a b, wärend zwee LEDs op der rietser Säit déi Ausgabe weisen.D'Resisateuren benotzt am Circuit sinn all 2,2k ohmen.Wann inputs a a b op an d'Ausféierung vun der Output, weist den Output, deen e binäre Wäert vun 10 ass, representéiert d'Zomm 2 (1 + 0 = 10).Den XAR Gates, wou mat den éischten 12 Iwwerniddene gebaut ginn, sou séier ewel am ënneschten Summe, während déi ënnescht Halschent vum Batden an oder oder oder oder Speziomobilien enthält.

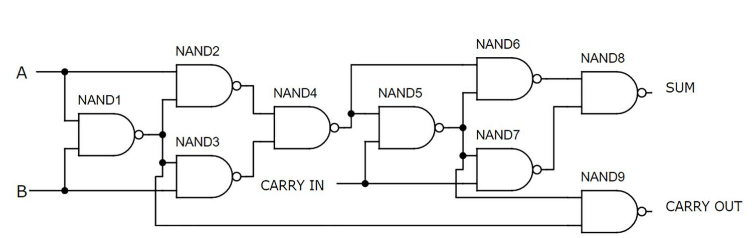

Voll Adder mat Nand Gates

Figur 7: vollem Adder mat Nand Gates

Dëse Stroum, deen néng Nandaafie benotzt, mat allen Schnéi gemaach ginn, déi ënner 30 Iwwerbegrëffer organiséieren den oviesch Transstatiounen aus Lëtzebuerg ginn.Dës Method ass tëscht den einfachsten an effizientsten Weeër fir e vollen Adder ze bauen mat diskret Komponenten ze bauen.All d'Gates ginn op der ieweschter Halschent vun der Broutboard zesummegesat, während d'Schalter déi ënnescht Halschent besat.D'Funktioun vun der Circuit ass bewisen mat Input a a b op an den Ausféierung, deen an engem Ausgangskrasse vun 10, gläichwäerteg ass op den Dezimalzuel.

Vollhändler mat Nore

Figur 8: Vollhändler mat an och Gates

Nei mat nénger Équipe ass intern Iwwerweisung ugestrach, ginn dëst Abups an dësem Ofgesamt a mam Goal.Eng voll Adder mat Oche ze bauen, bitt eng gutt Alternativ, awer eng méi komplex Wirbelen am Verglach zu Nand Gates.All Iwwerweisung an den Oche Gata ass begrënnt, mat de Sammler verbonne mat orange Jumper Drot fir selten an organiséiert Wirbelen.Dës Konfiguratioun gëtt mat Inpute a a b aktivéiert an de Cared-in desaktivéiert, féiert zu den Ausgaben, déi op d'Ausféierung aktiv ass an d'Zomm ass.

Mat dëser Ermëttléieregkeet vun Adder Technologie, vun der Basis Halschent a sophistikatinéierter Luterten Déift Dëst ass eventuell datt dës Komponisten ofdaucht sinn fir d'Fortschrëtter ofdaucht.Déi operationell Charakteristiken an d'Implementéierung Beispiller, déi d'Reguléierungsméiglechkeeten an d'Effizienz vun den Effiziener a verschiddener Behënnerung-Astellunge registréiert.Wann Dir d'Struktur an d'Funktioun vu Hëllef vun Hären aus hirencen, besonnesch duerch hiert Wiederpräisser an hiren Ofdrechnen, mir gewinnt Zouen an hire Kapitaléng.Dëst Wëssen ass instrumental beim Affiche fir den Design vun der méi effizient a méi séierer Berechnungssystemer ze beweegen.Opriichtung, Dépungen vereinfachen net nëmme mat komplizéiertererduücht- ugesinn, awer proufen et nach eng Prendératioun an der Dechnlechkeet wéi ënnerschiddlech gutt Veraarbechtung an der Datebank, an ziger Sektional Veraarbechtung.Wéi digital Technologie evoluéiert, déi lafend Verfeinerung an Innovatioun am Adder Design ass weider e Ecksteen an der Entwécklung vu méi fundamentalen Komponisten ze garantéieren datt d'Grondstoffsätz an der Ëmlafbunnstoffe sinn.

FROEN FROCESS [FAQ]

1. Wat ass e vollen Ukënnegungskuucht?

E komplette Verhaftung ass en digitale Circuit deen dräi binär Stécker bäidréit fir eng Zomm ze produzéieren an en Ausgang.Et ass entwéckelt fir d'Zousatz vun dräi Inputen ze verschaffen: zwee bedeitend Stécker an ee droen vun enger viregter Zousatz.Dëst erlaabt et an zwangsallstécker ze benotzen fir Multi-Bit Binär Zuelen ze addéieren.

2. Wéi vill an, oder, xor am vollen Adder?

En typesche vollen Haft enthält:

Zwee Xorpatten fir d'Zomm ze generéieren.

Zwee a paarte fir zu der Ausféierung vun der Ausgabung bäidroen.

Een oder Gate fir d'Ausféierung vum Ausgang ze finaliséieren.

3. Wat ass Droen Input am vollem Adder?

Den Droen Input (Cin) an engem vollen Adder ass den Duerchféierung vun der Zousatz vun der viregter leschter Persounen an der Multi-Bit Binary Zousatz.Et erlaabt de komplette Verhaftung dëst virdrun

4. Firwat benotzt e vollen Adder anstatt en halleft Adder?

E vollen Adder gëtt benotzt amplaz vun engem hallwen anere Adder well et kann dräi Ziti bäidroen (och d'Ausdrock vun der viregter Ergänzunge bäizefügen fir ze feelen fir ze feelen fir ze feelen fir ze feelen fir ze feelen fir ze feelen fir ze feelen fir ze fidderen an e vollen Erkenntnis ze ginn.En hallef Adder kann nëmmen zwee Stécker bäidroen an net eng Dispositioun hunn, déi eng Disponibilitéit hunn, wat limitéiert seng Benotzung fir déi einfachst Forme vu Binquenz ouni Squauungsverkaaft.

Deelen: