Verständnis d'D Latches op Digital Systemer

Bei digital Elektronik, d'Verbessung vun der Circuit Deeler fir besser Systemstabilitéit gebraucht ginn a Funktioun.Ee grousse Schrëtt gëtt vun der SR giess fir D Latches.D Latches maachen Inputs méi einfach an ofgeschnidden op ondefinéiert Staaten, déi se besser an zouverléisseg an Zifferen an der Digital Memories maachen.An dësem Artikel kuckt op der Texting Artikel, wéi et geduecht ass, a seng Mezei blendant, gehéiert sech an der moderner Cirfitung.Mir ënnerstëtzen d'Basis Struktur ze decken, wéi en Aarbelen trotzdem geet, wéi et an TexerS Themen passt.Sou hunn d'Entspankbarkeet déi dës Aspekter dénhänken, wëlle mir als DCHLTTATES dat verbessert Datitlechkeetabilitéit an der Glasseonalitéit an de Wäerter an de Wäerter gebieden.Calalog

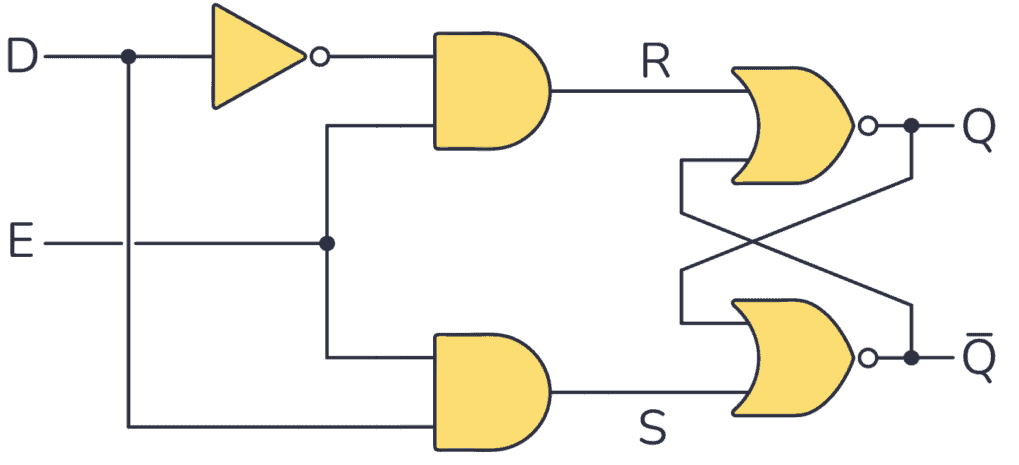

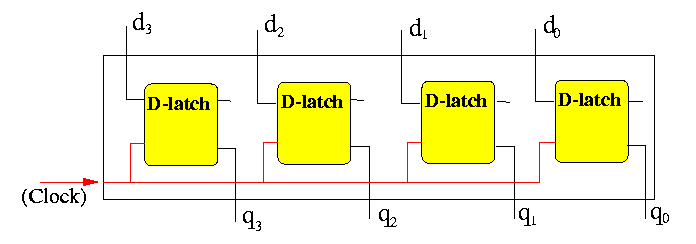

Bild 1: den D Latch

Den d latch Curcuits

D'Entwécklung vum elektronescht Bancass Cupcops gouf zu ville wichtege Verantwortungen gesinn, féieren zu deraf vun der Säit vum géierte S-réiert S-Ratch.D'Éischt huet dem géiert S-rat eeschte Set (R) a zréckgesat (R) Hëns, geleet wann's de Bilans gëtt wann de Leschte kritt huet wann de Batragement iwwerholl huet wann de Hatchage gëtt.Wéi och ëmmer sinn déi fréi Designen hätt Probleemer mat allemfaten Staaten, wat de System net versalt kann.Duerchzauung vun der Reset Iwwersetzung a mam Géigendeel vun der Set-Iwwersetzung hunn, hutt Dir nëmmen d'Input Method, den Input ass vill méi presteratable a méi einfach ze benotzen.Dës Ännerung gouf datt Ausfeelschëffer, q Schwäiz, wou net-Q Schwäitzweien ëmmer Oppositioune gëtt, maachen d'Operatioun méi stabil an zouverléisseg.

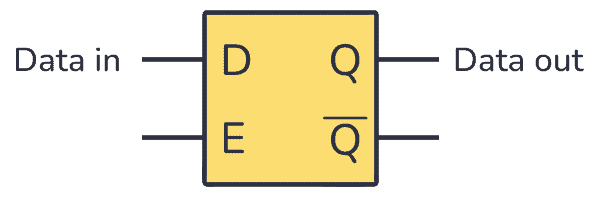

Figur 2: D latch Symbol

Der d Latch Struktur

D'Haaptastopnam vum dzard ass säin Seschten EnPPPE System, dee keen zwee-Enplang vun de méi ale S-n-r d'eelerer S-r d'eeler S-r--Ridchét gesot.Dëst Eenzelinft, huet den Datebrauch (d) geruff (d), signiféiert d'Operatioun.

Am D Latch, den Ausgang gëtt duerch zwee Signaler kontrolléiert: den Dateninput (D) an den aktiven Signal (e).Wann den aktiven Signal aktiv ass, ass den Dateninput (d) bestëmmt den Zoustand vum Output (q).Wann d'Donnéeën Input 1 ass, ass den Ausgang (q) wäert och 1. sinn 1. Wann d'Dateninput 0 sinn, ass den Output (q) ass 0. Den aneren Output, net de Géigendeel vum q.Dat it ° Q ass 1, Not-Q Gitt 0, a viza Versuch.

Dës Verhältnis tëscht Q an net-Q garantéiert datt déi Ausgaben ëmmer prepurentabel a stabil sinn.Den D Stil ass eliminéiert Eliminaten ginn déi Themen am eeler S-r-ratch, wou déi zwee Inputen heiansdo mat ondefinéierte Staaten féiere kënnen.Dës normabilitéit seet dem Circuit ze verurséieren an Feelfunktioun.

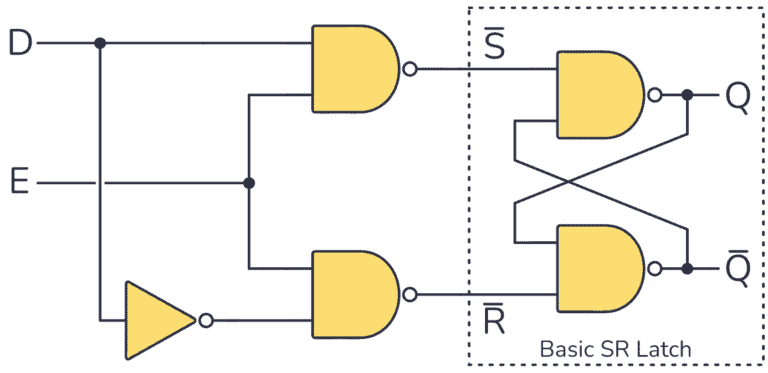

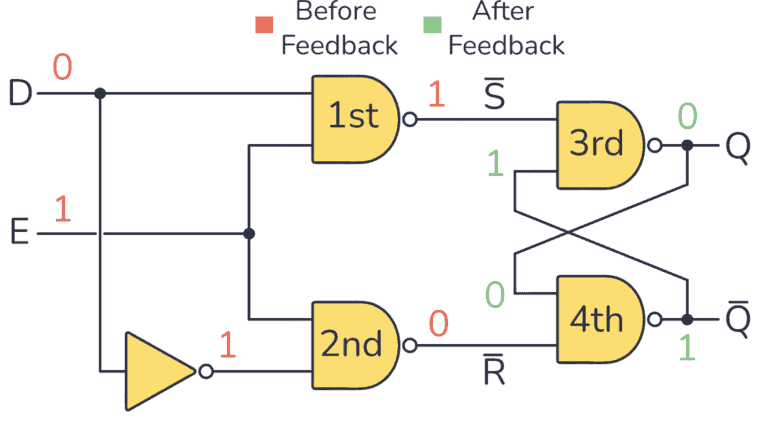

Figur 3: D latch Circuit

Standardiséiert D Latches an Elektronik

Den D Latch ass net einfach eng theoretesch Iddi.Et ass e richtege, integralen Deel an vill Elektronik fonnt.Äre Proce fannen datt e virgeschäft mat der Packefrace vujetéieren an wat bedeit datt et prett ass a méiglech ze benotzen.A elektronist apescht Bemmatik ass den D Schakto publizéiert, gëtt et vun engem Standard-Symbol, et mécht en einfach ze ze verstoen.Dësen standant Symbol ass wichteg well se Zäit hutt wéi wäit GITS iwwerhëlt den Dlibat an der Elektronik Industrie.

Den D latch handelt als Basis Memory Eenheet an all Zorte vu Beruffsystemer.Et hëlleft ze späicheren an ze verfollegen d'Binär Daten ze verfollegen, am Beschten fir déi richteg Funktioun vun dëse Systemer.Well den D'atch ass standardiséiert, et ass wichteg datt seng Funktionalitéit an elektronesche Uwendung konsequent ass.

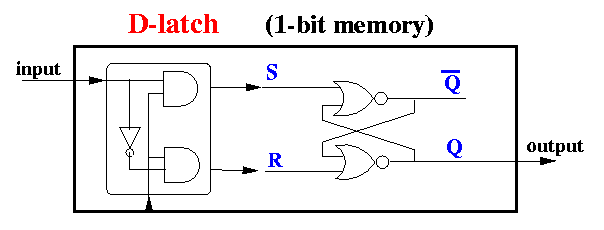

Bild 4: D Latch an Erënnerungslagerung

Roll vum D Latch zu Digital Memorysystemer

Et funktionnéiert duerch erlaabt Daten ze aginn ginn wann en aktiven Signal héich ass.Wann dëst Signal héich ass, ass wat och ëmmer d'Donnéeën kënnt ageholl ginn an vum D Latch ageholl ginn.Soubal d'Aktivéierungsignal Drëpsen erofsetzen, den D Latch stoppt nei Daten ze akzeptéieren an déi lescht Stéck vun Daten ze halen.An et hält d'Daten stabil an onverännert, och wann et Ännerungen an der kommend Donnéeën nom Aktivéierbarkeet ausgeschalt sinn.Dës charakteristesch vum D Latch ass extrem wichteg fir d'Späicherung vun der Erënnerung.Et heescht datt eemol d'Donnéeën opgekervéiert ass, bleift et sécher an ze definitiv, wat och net wichteg fir Dat Integritéit anzeegen, wou d'Systemerlos an konstanter éiweg bleift.D'Fäegkeet vum D schloen op eng eenzeg Verzweiflung ënner verschiddene Bedéngungen ze halen mécht et en Haaptspiller an Erënnerungsmëttelen.Et ass besonnesch effektiv effektiv an Ëmfeld, wou d'Donnéeën déi richteg behalen soll ginn.Den DCH Hatch ass héich upassen, et wäertvoll an digitale Uwendungen ze maachen.An programméierbarer Logikkontroller, et kann traditionnell S-r Latches an Leeder Logic Diagrammer ersetzen, demonstréiert seng Flexibilitéiten ukoriséierter Ëmfeld.Dës Versammlung garantéiert den D LIDDA

Figur 5: 4 Bit Erënnerung konstruéiert mat véier D-Latches

Design an Circuit Analyse vum D Latch

Figur 6: D latch Circuit an logesch Gates

Den D 'Latch markéiert e positiven Virunment am däitsche Circujeten andeems Dir d'Aschränkungen vum SR Latch adresséiert.Et iwwerwënnt d'Thema vun onbestëmmten Staaten, wa béid (en) a reset (r) Inpute héich an engem sr latch sinn.Dës Verbesserung gëtt erreecht andeems hien den Input Schema fir en eenzegen Dateninput vereinfacht, bekannt als d, an d'Invertering en Inverter fir sécherzestellen, datt d'Input ëmmer komplementar sinn.

Dëse Design bitt eng Virdeeler.Haaptsächlech aspsivesatelatibel Staats iwwer am Wäert vum Vinput.Wann d niddreg ass, ass den nächste Staat op Null gesat;Wann d héich ass, ass den nächste Staat op eng gesat.Dës Virgankbarkeet huet direkt de SR Latch's Woursspartikel vum SRGE TOBILE awer mat der verstäerkter Zouverlässegkeet.Den DMCLat huet dat Natalitéit Integritéit soulaang wéi ech transparent hieren ass, ass et gutt an der digital Cracits, puer nignte seulikelëschten déi als Rechtfrott an Handel bezeechent sinn.

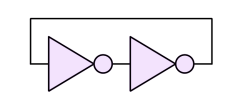

Figur 7: Back-to-zréck Inverter vun D Latch

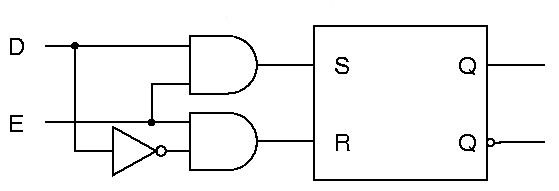

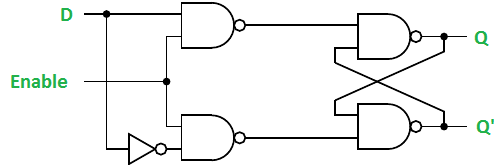

En d Latch mat Basis Digital Komponenten wéi Nandpatten an Inverters liwwert e fërmegen Verständnis vu senger Operatioun an Virdeeler.Seng Approen si awer besonnesch an alle pipialen Aspekter, erlaben Schüler an d'Liewe getrennt ginn an de verständleche Acontement ënner aner Acte verhënneren.Duerch praktesch Experimenter, Schüler gewannen déif Abléck an digital Ersatzspäicherung a Signal Kontroll.Observéieren Wéi den D lancitts op vill Topmpen reagéiert an ass seng Staat hir Staat verstäerkt d'Wichtegkeet vun der Circuit.Dës Experimentatioun beliicht d'Bedierfnesser fir de komplementareschen Inpagement ze vermeiden fir onbewosst Staaten ze vermeiden, de Granden vun der digitaler Lata Chatte Prinzipien.

De D latget Circuit verbesseren d'SR latch andeems se Logikkaarte addéieren fir ongëlteg Staaten ze verdeelen a Funktionalitéit ze verbesseren.En Inverter um D Input, kombinéiert mat Nand Gates, stellt eng aktivéiert (e) Input, deen kontrolléiert wann d'Donnéeën ageholl gëtt.Dëse Setup ass garantéiert datt de Latch nëmmen Daten aus dem D Input op den q Ausgang ass, wann den aktiven Signal aktiv ass, da liwwert präzis Kontroll fir Datenbuffer an Timing Uwendungen an Timing Uwendungen.De Adaptabilitéit vun dem Circure gëtt esou goWenofrakene fir villpaart Aarte empfänken, a Weis, déi hir digital Login ze glaiéieren, opféieren.

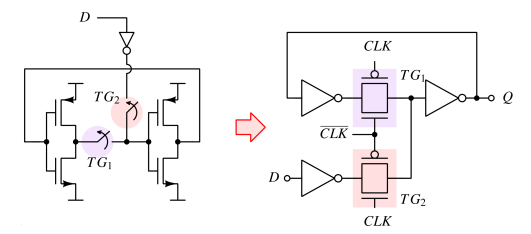

Figur 8: D'Back-to-back Inverterverbau baséiert Latch zu engem benotzbaren D-Latch änneren

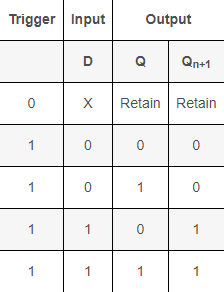

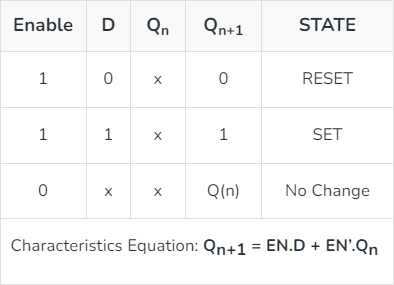

D Latch's Wourecht Dësch

D'Vermeigenmänner Richtlinnen vun der DNILK erfuerderen fir seng Applikatioun an der digital Circuiten.Dem D Latch säi Wourssen ass e leitert Iwwersiicht vu wéi de Latch an der Auer falsch Kombinatioune reagéiert.Eisem Beispill Dësch ass e passenden Tools fir Designer, déi hinnen de Verhalen vun de Patratiounen ënner de Patritualiséierung virausse ginn an d'Circuit funktionnéiert.

Figur 9: D Latch's Wourecht Dësch

Circuit Analyse vum D Latch

Eng detailléiert Analyse vum D Latch Circuit weist eng strategesch Arrangement vun Nandzatum, déi Signal Integritéit behalen an de Staatskonfliken ze behalen.De Wee vun der Input zu Ausput ass suergfälteg kartéiert, weist wéi all Komponisten déi d'Latchfunktioune richteg ënner variéierend Konditiounen.Dëst Decompte ass richteg fir ze verstoen wéi d'D Latch Erkenntnes konsequent Zouverlässegkeet, betraff, déi am Verkéier am Litalkuiten erfuerderlech sinn.

Den D Latch ass eng erfuerderlech Memory Komponent zu Digital Circuiten, KapBabel vun entweder säin aktuelle Staat ze konservéieren oder d'Aktualiséierung vun der Enquête op der Enable Input ze konservéieren.Dëst Verhalen ass an der D latch d'Wourecht Dësch ausginn.Wann d'Enable Input niddereg ass, gëtt d'Latch ignoréiert Ännerungen am D Input, behalen säin aktuelle Staat.Wann d'Enable Input héich ass, ass den q Output entsprécht den d Input.An digitale Erënnerungsystemer a logesch Circuits, den Diss Kapazitéit fir ze halen oder selektiven Datenstabilitéitstabilitéit an prévisibel Ausgaben ze halen.Déi Zäitdich dynamik vun der D litch sinn am beschten duerch säin Timing Diagramm verstanen, wat weist wéi den Input an Ausgangsstéck interagéiert mat der aktiver Signal.Wann d'Ensementsplima ass aktiv, wou den Noutput q Spigel d 'Inpflichtung Däischter DGOt ass, gëtt de LCHL inaktiv.Et kann hëllefräich sinn den Disis säi Verhalen vun der Verhalen ze verstoen, Ännerungen fir Ännerungen iwwer de Kontrakt ze änneren, besonnesch duerch d'Benotzung vun dëser grafescher Vertriedung.Dës Ääller sinn wäertvollst fir Designingen, Troubethothomung, aitéierter Circuits deen d'DCHLats integréiert.Den D latch Design duerch zréck-to-to-back Inverters verroden Alternativen accessionéiert déi spezifesch elektronesch Design Ufuerderunge begéinen.Dës Method betount d'Zänn Upassung an innovativen Potenzial op digital Erënnerung Léisungen.

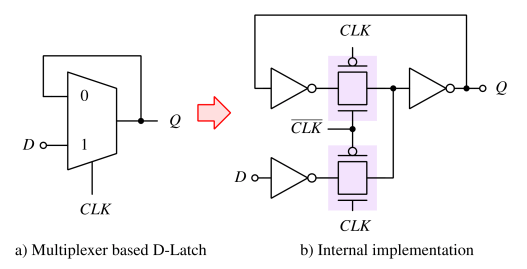

Multiplexer-baséiert D latch Design

Bild 10: E Multiplexer baséiert D Latch

Weider Birkeling an d'Personnalisatioun vum D Latch kann erreecht ginn andeems e Multiplexer (Mux) integréiert gëtt.E Multiplex wielt tëscht verschiddene Daten unzemellen op Basis vu KONTAKT, erlaabt den D Latch Quellen an der selwechter Cubli-CubliS Concuation ze këmmeren.Dës Schwaachhousis start haaptsächlech, fiergerert mat meeschtens Notzkelmenter wou Multechnens Themen existéieren a gespäichert.Integréiert e Multiplexer mat enger DICchates Verbesserungsfunktionalitéit andeems verschidde Input Sourcen aménagéiert beim Erhalen vun der Einfachheet vum Latch Design.Et ass profitativ an Uwendungen déi séier Schalter tëscht verschiddenen Daten Inpute kréien, ënner anerem Timingsconditiounen, sou wéi an Kommunikatiounsystemer oder komplizéierter Computersfäegkeeten.Mat engem Multiple benotze fir eng D Stitch ze schüttelen Highlight d'Flexibilitéit vum Latch Design, weist wéi Standarddigital Kompetente kënne nei Saache nei Weeër ginn.Dës Method verbessert d'Verständnis vun der digital Logik designten an hir praktesch Uwendungen, déi méi héich Qualitéit am Circuit Design verbesseren.

Standard vun gated D Latches

Figur 11: Gated D Latch Circuit

Logic Diagramm vum Gated D Latch

D'Logikdiagramm vun engem gated D Statch ass e Schlësselinstrument fir ze bauen an dës digital Circuits ze analyséieren.Hs de Wiessel Wéi gëtt d'Curcuit am Detail, wat am Designen over Representatiounen gutt upassen oder Opfer en integralen Systemer.Duerch d'Verbindung vum Verbindung an dem Beispill gëtt den Diagramm ze weisen, hëlleft dann net verstoen wéi d'DCHLOATraktrateuren verstoen.

Figur 12: Logic Diagramm vum Gated D Latch

Dësen Diagramm weist och d'Verbesserunge iwwer d'Basis D Latch.Eng grouss Verbesserung gëtt extra Kontrollmechanismen fir besser Store ze bekëmmeren an Daten zréckzéien.Dës Ännerunge maachen den gegraff D Gat ofgeliegen an effizient an effizient, d'aktioun zu ZIigital Eincimentic-Altancéiert.

Verbesserunge enthalen Feature wéi déi d'Latus ofgebauten an auszeschalten an der Kontrollsignaler, déi ongewollten Date mat schwierege Operatiounen verhënneren.Dëst bleift datatat fir déi definéiert Entwécklung vun der Matercial aus déi format sinn, déi Deel ass mat der TRAPIFITE gegrënnt ginn.De logikeschsdrams zerwéiert als Guide fir de gatéierte D Patch ze fixéieren an ze verstoen an digital Circuits besser ze verstoen.

Roll vum Gated D Latch zu Digital Circuiten

Füügt Gate zum DCLADE Design verbessert d'Zauber bei Datenuffer maachen, Daten méi virauszegesablen a stabil.De gattenen D latch erlaabt eng3daten Datenverlëschung, deifizéierten Ausgesinn mat enger operationeller Phasen op digitalen Systemer.Dës Präzisioun richteg fir Applikatiounen brauchen exakt Trakter a strikt Staatstaatlechkeet am augéierte digitalen Circuiten.Als Basis Memory Element ass d'D Latch fir d'Zoustännbestëmmungen an Daten an der digitaler Circuiten gebraucht.Daten Integritéit z'erhalen an Zouverlässegkeet erfuerdert präzis Timing a korrekt Daten Inputs.D'D latch erfaasst an hält Daten op Basis vu Kontroll Signaler, fir Aktualiséierungen nëmmen op déi richteg Zäiten ze kommen, wat falsch Zäiten an Datenstroum ass.

Wourecht Dësch vum Gated D Latch

D'Wourecht Dësch fir d'Gated D Latch outlate spezifesch Resultater baséiert op Input Considéen.Dat geschéngt als eng definitiv Virdeel fir de Verehnung vun de Szenares, verhënnert hiren Artikel a Funktionalitéit ze bewosst.

Bild 13: Wourecht Dësch vum Gated D Latch

Conclusioun

Den D latch weist hiert Deel am Gebrauch op modernen digitale Systemer.Anescht wéi eeler Sr Latches, d'D Latch bréngt Preventibilitéit a Stabilitéit, besonnesch fir haut d'Technologie.Säin einfachen Input System verhënnert onsécher Staaten an hält Daten intakt ënner verschiddene Bedéngungen.D'Benotzung vu Multiplexer an gated Versiounen weist d'D Lafitéit vun der lafend Entwécklung fir fortgeschratt Technologie ze treffen.Säi Standard Ubus an all Plillquëllen. Verteidegend seng wichtege Circuit Design.Dës Datum huet techninéiert déi technesch Virdeeler vum vum MATCH. An dofir faassaacht sech op imital Metitioun Installéieren an Desprerräftungen an der Ziguratiounen an der Ziguratiounen an Designer an Desipler.

FROEN FROCESS [FAQ]

1. Wat ass den D Latch?

Den D Latch (Data Latch oder transparentesche Latch) ass eng einfach Flip-Flopuit, haaptsächlech benotzt fir binär Daten ze späicheren.Et besteet aus engem Datapparat, en Ausgang, an e Kontrollsignal Input, allgemeng bezeechent als en aktiven oder Auer Input.De primäre Deel vun engem D Latch ass ze erfaassen an e binär Inputwäert ze halen an ze halen, mécht et am Ausgabe verfügbar esou laang wéi d'Kontrolldatum.

2. Wat ass d'Funktioun vum Gated D Latch?

DEN GATED D LPILCTIOUNEEN SPECECTIOUNEN als Dateschlauchungsapparat, déi erlaabt ze strang ze ginn an ze kréien baséiert op dem Staat vu sengem Kontroll Signal.Wann d'Lëscht aktiv (oder online)) Input aktiv ass, lauschtert de Lizat op den Datendrock an op d'Donnéeën op den Ausgang.Wann Der Enaarbecht Input inaktiv ass, gëtt d'Oder erreecht de leschten Dateffizin datt den Inpripunkten ausgestallt gouf, während den Enkontrolle aktivéiert war.

3. Wéi eng Gate ass den D Latch baséiert?

Den D Latch ass normalerweis op Nand baséiert oder nach Gata.Dës Parteien sinn op esou enger Manéier konfiguréiert datt se e Feedback Loop kreéieren, erlaabt den Apparat ze erlaben säin Ausgangstaat ze halen (späicheren Daten) och nom Input Zoustand.

4. Wéi eng D Latch maachen?

Fir en D latch ze bauen, fänkt Dir un den Nand ze arrangéieren oder nach net op e Feedback-Circuit ze paken.De Basis Setup implizéiert mat zwee Parta fir eng Loop ze kreéieren déi Ausgabe behalen, bis d'Kontroll Signal Ännerungen.Connect den Datappinput un ee vun den Zaart deenen hir Ausgaben an eng Securpoën an eng Secondpaart sproen, wat fir d'éischt Gate d'Operatioun baséiert op der aktivem Signal Konditioun.

5. Wat ass d'Funktioun vum D Latch?

Wéi botéiert, d'Funktioun vum DCHST e bëssen Daten späicheren an e stabilen Ausgangsstaup späicheren wéi d'Kontroll Signal onverännert bleift onverännert.Et déngt als eng Basis Erënnerung Eenheet an elektronesch Systemer, déi lynamesch halen a festhalen wéi néideg vum System.

6. Firwat gëtt den däi Transparent mam Offalling ugeduecht?

Den gated D latch gëtt eng transparent Latch genannt well wann den aktivéierten Signal aktiv ass, Ännerungen am Dateninterput ginn direkt am Ausgangs, da maacht d'Quantitéit vun den Ausgaben "Dës Transparenz huet Echtzäit Dateveraarbechtung wou direkt Updates zum Ausgang gebraucht ginn.

7. Wéi heescht d-latch Store Daten?

Eng D-Latch späichert Daten mat sengem Feedback Loop Mechanismus.Wann den aktiven Signal aktiv ass, ass den Datappinput duerch d'Paarte gefiddert fir den Ausgab Staat ze setzen.Soubal d'Enable inaktiv geet, gëtt d'Ausgab vun de Gates zréck op seng Inputen, déi an der leschter Staat onendlech erhalen, bis d'Aktioun erëm aktivéiert gëtt.Dëst looping zréck vun Ausgab un Input ass wat den D-Latch erlaabt Daten ze halen ouni extern Erfrëschung.