De Spi domystified exploréiert d'Grondlage vu Serior Peripherie Interface

De Serior Peripheral Interface (SPI) Protokoll ass als Ecksteen an der Räich vun digitale Kommunikatioun erfuerdert, déi de Roubusen erfuerdert.Ursprénglech entwéckelt fir Seindeldesch Dateinumm tëscht Mikkontroller a Peripheral Apparater ze erliichteren, d'Spai ënnerscheet.Dëse Protokoll beschäftegt e Master-Sklaven Architektur, notzt véier Haaptleitzuel-Master aus, Sklave an (Mosi);Master an, schloen eraus (Miso);Auer (Sck);a Sklave Wielt (SS) -To -To -To Etabléiert eng kontrolléiert an effizient Ëmfeld fir Dateniwwerdroung.Entworf duerch eng Vuessulatur eng Chancegielfristeg Modi a Konfiguratiounen, ëm 3-Dras- a Mori-II-Zoufall, z'ënnerbriechen, aprobend Elektresch Demanden, a Konsumentesch Uwendungen.Doduerch wéi mindeleghorstellungs-Dëwen an déi technesch Inrianies vum Spi kënnt, diskutéieren aner Konstruktioun, matgedeelt Deeler Phreial, an der moderner misse fir d'modernem elektronesch Designen a Systemer.

Calalog

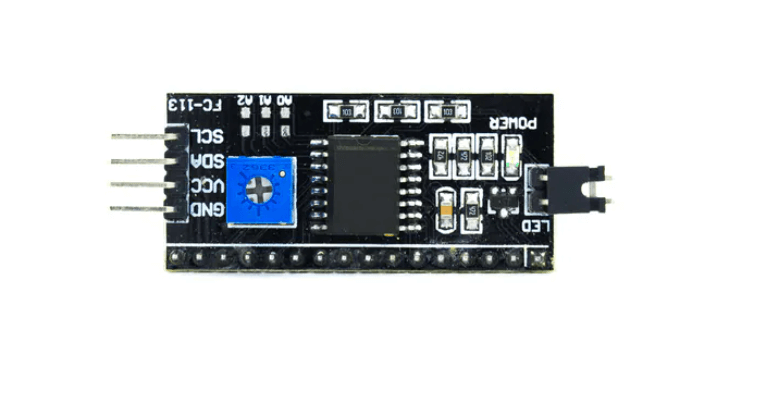

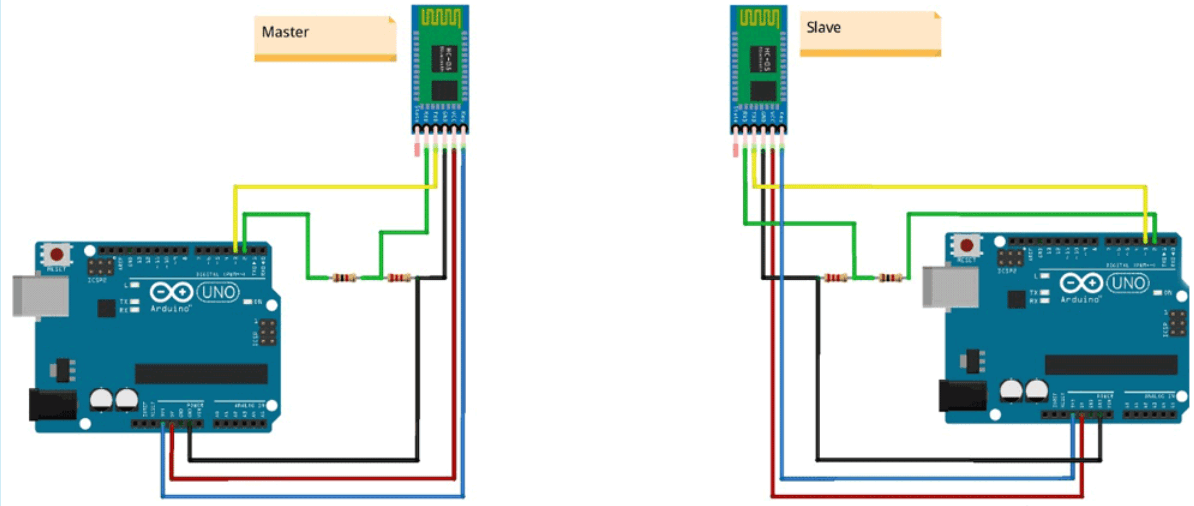

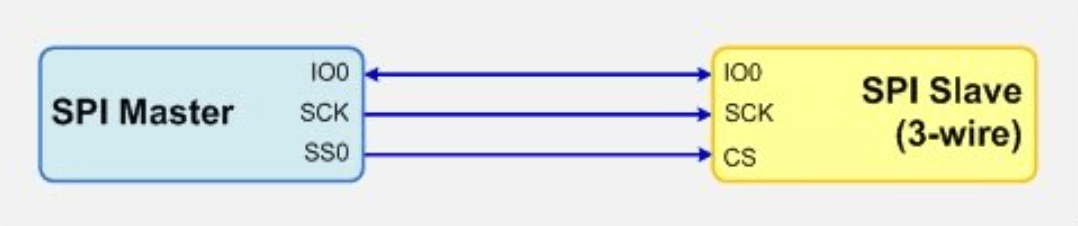

Bild 1: Serial Peripheral Interface (SPI) Bus

D'Fäegkeeten an d'Charakteristike vu Spi

De Serior Peripheral Interface (Spi) Bus ass Schlëssel fir séier, voll-Duplex, synchroneschen Datentdransfer tëscht engem Masterapparat a Multiple Gerät.Onerwënscht aner Protokollen, Spi benotzt véier Haaptdate Linnen: Master eraus, Sklaven an (Mosi), Master in, blave out (Miso), a Skack), a Skack), a Skack)Dëse Setup erlaabt effizient a robust Datenhandlung fir verschidden Uwendungen.

Bild 2: Master-Sklave Konfiguratioun

An engem Spi System fléisst Daten gläichzäiteg a béide Richtungen, erlaabt echt Kommunikatioun.De Master schéckt Daten un d'Sklave iwwer d'Mosi Linn a kritt Daten aus dem Sklave duerch d'selwecht Zeil gläichzäiteg.SPI Geräter kënnen Daten iwwerdréinen, déi mat entweder bedeitendst bëssen ufänken (MSB) oder am mannsten bedeitendsten Bit (LSB).Dëst erfuerdert virsiichteg Konfiguratioun no dem Datatchet fir déi richteg Stéck Sequenz ze garantéieren.Zum Beispill, zu Arduino Projete, no Portekonfiguratiounsberäich

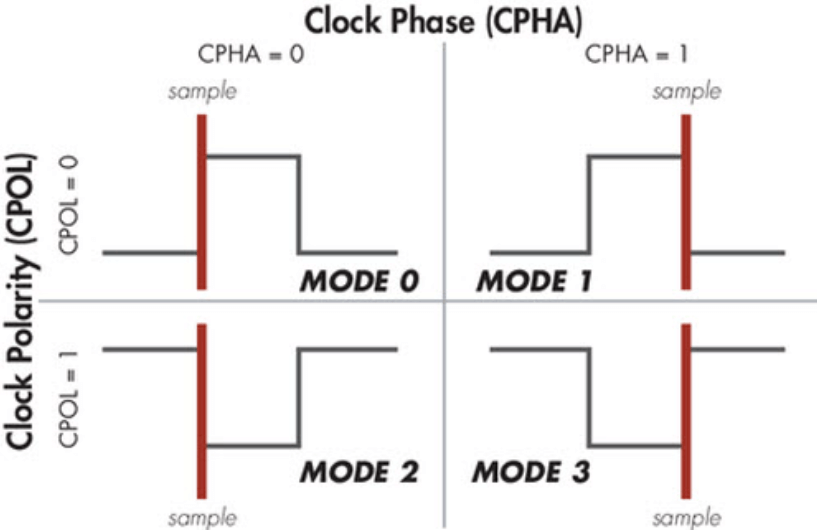

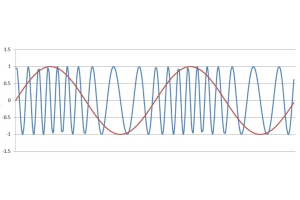

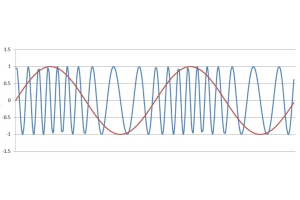

Figur 3: Clock Polaritéit a Phas

D'Genauegkeet vum Datentransfer a Spi hänkt vun der Auer of, déi d'Auer Polaritéit (CPOL) a Phas (CPA) aussetzt, wéi eng Daten Stécker gemaach goufen, wéi d'Donnéeën a Kommunikatioun aussetzt.SPI ënnerstëtzt véier Modi fir verschidden Timing Bedierfnesser z'empfänken:

• Mode 0 (CPOOL = 0, CPP = 0)

D'Auer ass Idle niddereg.Donnéeën Stécker ginn op der Clock Rand opgefaang an op de gefallende Rand weiderginn.Daten musse prett sinn ier d'éischt eropgaange Clowpuls sinn.

• Mode 1 (CPOL = 0, CPP = 1)

D'Auer ass Idle niddereg.Date Bits sinn op der gefallem Rand gefaang an op der nächster erop eropgeet.

• Mode 2 (CPOL = 1, CPP = 0)

D'Auer ass idle héich.Daten sinn op der gefallem Rand gefaangen an op der opgeruff.Daten musse prett sinn ier déi éischt gefallendem Clowpulse sinn.

• Mode 3 (CPOL = 1, CPP = 1)

D'Auer ass idle héich.Date Stécker ginn op der opgestan Rand ageholl an op de fallen Rand iwwerdroen.

All Mätscher garantéiert Datategreifheet andeems genau Dateine mat enger Plaz Transvis mat enger Plaz iwwerdikt, verhandelt dat Ferurpositioune tëscht Make-Offeren.

Glänzend vun Schlësselbedingungen

Fir d'Spioun Protokoll ze verstoen, ass et néideg déi folgend Schlësselbedingunge ze wëssen, déi den Apparat Interaktioune definéieren:

CLK (Serial Auer): Dëst ass den Timing Signal, kontrolléiert vum Masterapparat, dat bestëmmt wann d'Donnéeën a Kommunikéiert ginn a Kommunikatioun.Et setzt de Rhythmus fir Daten Iwwerdroung iwwer de Spi Bus.

SSN (Sklave Wielt): Dësen aktive-niddreg Kontroll Signal, huet vum Master gelongen, wielt den aktiven Sklave Gerät fir d'Kommunikatioun.Wann dëst Signal niddereg ass, weist et datt de Sklavapparat prett ass Daten ze kréien oder Daten op de Master ze kréien.

Mosi (Master eraus, Sklaven an): Dëst Datekanéit schéckt d'Informatioun vum Master un de Sklave.Daten fléisst duerch dës Zeil no der Auer Signaler, entstinn datt Stécker sequentiell vum Master zu engem oder méi Sklaven iwwerdroen ginn.

Miso (Master In, Sklaven eraus): Dëst ass den Datefwee fir Informatiounen aus dem Sklaven zréck an de Master ze schécken.Engesammelt d'Mosini-Eliceing En zwee-Eskdate Datendencheren an dem Spi-urade.

CPOL (CPOCK POLARGARGE): Dëse Astellung bestëmmt ob d'Auerleitung héich oder niddreg ass wann keng Daten Iwwerdroung ass.Et beaflosst d'Stabilitéit vum Idle Staat a Bereetschaft fir déi nächst Daten Iwwerdroung.

CPP (CLOCK Phase): Dëst Spezifizéiert wann Daten solle sample sinn - entweder op der Auer vum Zyklus am Ufank vum Zyklus oder de Rand geschitt, deen an der Mëtt vum Zyklus geschitt.Et ass de Schlëssel fir z'inignéieren Date Stécker präziséiert mat Clockpulsen.

Mastering Connectivitéit mat Sklave Wielt an Daisy Kettenmethoden

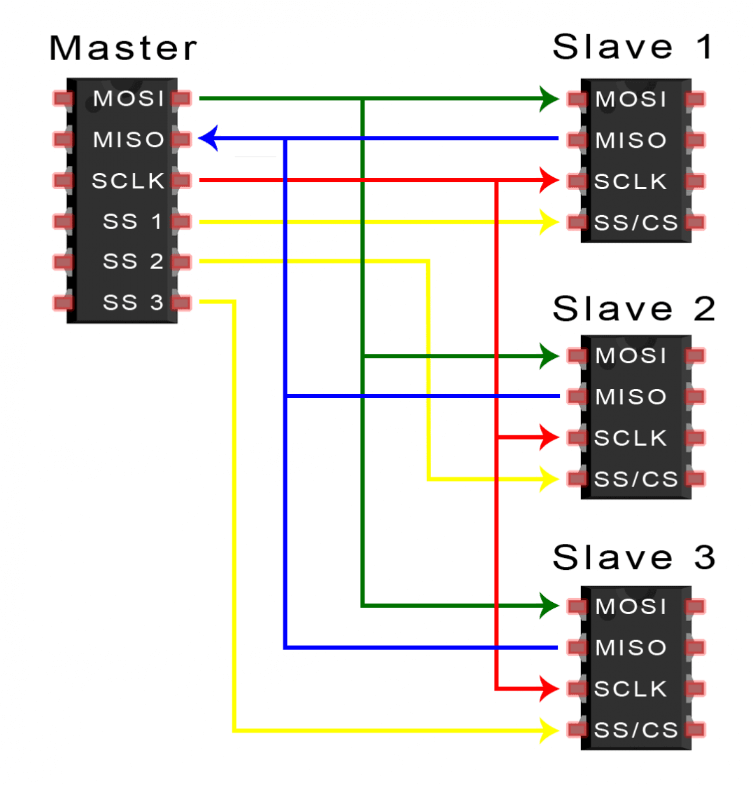

Bild 4: Multiple-Sklave-Select Conication

Wann e Master Spi Apparat mat multiple Sklaven kommunizéiert, huet all Sklave säin eegent Sklave gewielt (SS) Linn.Dëse Setup verhënnert d'Date Kollisiounen a garantéiert datt Kommandoen oder Daten vum Master nëmmen déi virgesinn Sklave erreechen.Nëmmen eng SS Linn soll gläichzäiteg aktiv fir d'Konflikter op de Master ze vermeiden, blaven eraus (Miso) Zeil, déi korrupt sinn.Wann d'Kommunikatiouns Kommunikatioun vu Sklaven net gebraucht gëtt, kann de Master d'Multiple Linnen aktivéieren fir Kommandoen oder Daten op verschidde Sklaven ze kréien.

Fir Systemer brauche méi Sklave Geräter wéi déi verfügbar I / O Pins um Master, ech / O Expansioun mat Hardware wéi e Dekorder oder dem Dammeiplexer (zB) benotzt. 238)Dëst erlaabt et een eenzege Meeschter ze managen fir vill Sklack effizient ze dedecken andeems se e puer Kontrolllinnen a ville SS Linnen dedecken.

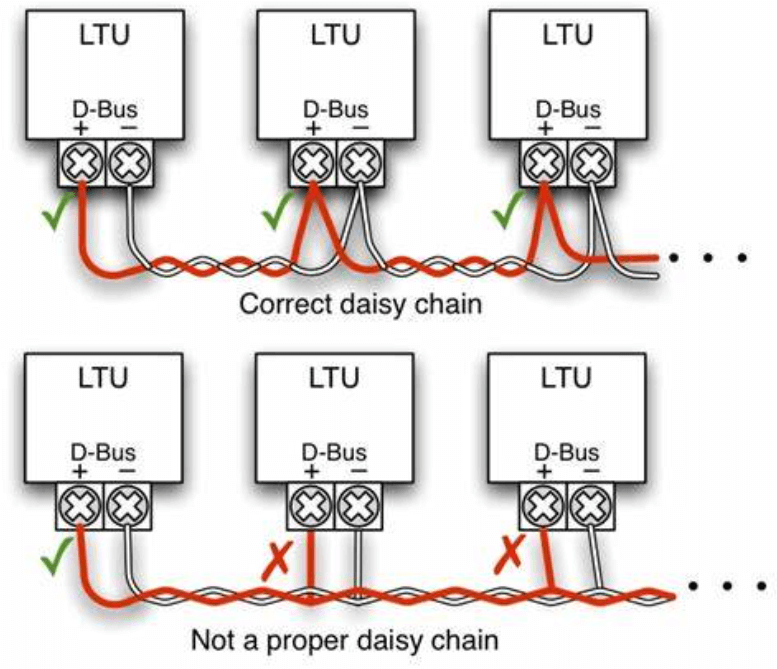

Figur 5: Daisy-Chain Konfiguratioun

DAISY-KANIN Konfiguratioun

D'Daisy-Kette Toopologie verbënnt Multiple Sklawer an der Serie, mat enger eenzeger SSS Linn benotzt.De Meeschter schéckt Daten op déi éischt Sklave, déi et verschafft an et op déi nächst Sklave verschafft.Duerfir drun, wat kann een Daten zréck op de Miskrol Zeil schécken.Dës Konfiguratioun vereinfacht Auswräier a gëtt nëtzlech fir d'Applikatiounsfäffe wéi sequitalifizéiert Artraoe gerëss well all den Apparat no dësem Viraussetzungsdirektiv voll ass wéi all Päsidentitéit si ginn.

Dës Method erfuerdert präzis Timing an Daten Ëmgank fir all Sklave korrekt ze garantéieren an d'Daten weiderginn.De SPI Master muss sech kennegeluesch managen d'Auer an Daten fléien fir Propagatiounspersonnagen an de Setupzäiten fir all Sklave an der Kette ze kréien.

Strategien fir effektiv Programméierung am Spi

Programméiere fir d'Spir implizéiert Mikrocontroller mat agebauter Spir Periphere fir Héichgeschwindeg Daten Transfer z'aktivéieren.Fir Arduino Benotzer ginn et zwee Haaptsäit fir d'Kommunikatioun ëmzesetzen:

Mat Hëllef vun Shift Kommandoen

Déi éischt Method benotzt d'Verréckelung () a Shiftout () Kommandoen.Dës Software-Driven Kommandoen erlaben Flexibilitéit beim Wiel vun Pins a kann op all digital I / O Pins benotzt ginn.Dës Geleabilitéit nëtzlech fir verschidde Hardware Setups.Wann dës Methodunge steet op der Softgendo fir méi Partizinatioun ze verschaffen, an ze tningen, ass et op Hardware-Verdreiden am Vergeigert

D'Spiebibliothéik vereinfachen

Déi Geschicht Method ass méi effizient a imklusiv ze verbannen mat der Sphatier ze kréien, déi direkt den Arduino säin Arduino's Onarard Forkarard uarden.Dëst resultéiert vill méi séier Datenaustauschsätz.Wéi och ëmmer, dës Method beschränkt d'Benotzung fir spezifesch spi-designéierte Pins vun der Microcontroller definéiert.

Wann Dir Programméierungskëscht benotzt, ass et bedeitend fir de verbonne Gerät vun hirem Datatchet ze verfollegen.Dëst beinhalt d'Astellung vun der richteger Bit Uerdnung (MSB oder LSB First) a genau konfiguréieren an d'Auerphasatioun (CPA) a Polaritéit (CPOLary).D'Spiebibliothéikbibliothéik am Arduino bitt Funktiounen wéi Set Bandorder (), Setdatamod (), a Setivider () fir dës Parameteren ze passen, fir gülteg Interaktiounen ze kréien.

Fir Arduino Borden, managen de Chip Wielt (CS) PIN ass e Must.Eeler Brieder, sou wéi den Arduino Uno, erfuerderen manuell Kontroll vun dësem PIN fir unzefänken an d'Kommunikatiounssessiounen ze starten.An Differenz, nei Modeller wéi den Arduino weider Offer automatesch CST Kontroll, maacht Spiopratiounen méi einfach a méi zouverléisseg.

De Spi Bus konfiguréieren: 3-Drot a Multi-Io Setups

De Spëff Prothol geschitt.

Figur 6: 3-Wire Konfiguratioun

3-Wirkonfiguratioun

Den 3-Wirmodus kombinéiert de Master aus, Sklaven an (Mosi) a Master an, geschloe ginn (Miso) Linnen an eng eenzeg batrifiger Dateitlinn.Dëst reduzéiert d'totaler Zuel vun der generaliséiert Pins op dräi: déi kombinéiert Datenlaang, d'Auer Linn, déi de Sichen )'t erméiglechen d'Linn vum Schnäpp (klet Linn.Operéiere an halp-Dulexmodus, kann dëse Setup entweder Daten schécken oder schécken, awer net all gläichzäiteg schécken.Wärend dem PIN GRANCRIGUE fir Geräter fir Geräter mat limitéierten GPio Disponibilitéit ze reduzéieren, da limitéiert dëst Setup ochEt ass gëeegent fir Applikatioune wou sporréieren Raum an hardware Simlicitéit ausqualitéite wäerten, an héichgeschnolldivddivission ass manner geféierlech.

Figur 7: Multi-Io Konfiguratiounen

Multi-io Konfiguratiounen

Wulti io Konfras, och driwwer an Doden Ia Bären, Expel d'Datewenn Zeilen déi op di traditionelleg Spi gesammelt ginn.Dës Verzeechnes benotzen zwou oder véier Zeilen fir Dateniwwerdroung, erlaabt Iech fir vill méi séier Datenpräisser andeems se gläichgelooss ginn.Dës Kapazitéit ass besonnesch empfindlech an héich Leeschtung vun der Ëmfeld wou d'Geschwindegkeet regéiert.

ual i / o: Benotzt zwee Datenlinnen, effektiv verdankt den Datentransferniveau am Verglach zum Standard-Line-Linn Setup.

Quad I / O: Egal beschäftegt véier Datenlinnen, bedeitend eropgaang duerch d'Effizienz.Dëse beschreiwt den Modus souwisou effektiv fir auszefellierrumzéiers den Organer (Xip) vun engem net flladesche Matiitatiounen, wou d'Markethëlstellung wéi d'Donnéeë iwwer all véier Linnen gläichzäiteg opdroe kënne ginn.

Dës verbessert ech / o Modi Bréck de Spalt tëscht traditionelle Parallel Interfacen, déi normalerweis méi Pins fir vergläichbar Datepräisser a méi pin-effizient Serien Setups.Duerch d'Erhéijung vum Zuel vun den Datenslinnen, Multi-Io Konfiguratiounen Boost Leeschtung wärend e Gläichgewiicht tëscht PIN Grof a operationell Effizienz z'erhalen, se maachen Gëeegent fir eng breet Palette vu héije Geschwindegen Daten Uwendungen.

Eng einfach Spi fir Transaktioun auszeféieren

Eng Schreifweis Transaktioun op d'Spi Flash Memory ëmfaassen, déi präzis Kommando Sequenzen an der Datiänzitéit an effektiv Kommunikatioun tëscht dem Masterapparat sinn.D'Operatioun fänkt mam Master z'aktivéieren d'Sklave Wielt (SS) Zeil, signaliséiert d'Zilplack fir eng Kommunikatiounssitzung unzefänken.Dëse Schrëtt ass Kär wéi et de spezifesche Sklavapparat virbereet fir Daten ze kréien.

Nodeems Dir d'SS Linn aktivéiert hutt, schéckt de Master e Schreiwen Kommando mat den erfuerderlechen Donnéeën byts.Dëse Kommando wielt normalerweis d'Aktioun ze duerchgefouert, sou wéi 'Schreiwe Statusregistrement,' gefollegt vun den Datebutschinnen den neien Inhalter vum Register.Prcistisiven an dësem Schrëtt ass dynamesch;all Feeler am Kommando oder Daten kënnen zu falschen Konfiguratiounen oder Datenkriptioun féieren.An och d'Six bleift d'Myto an engem héijen Défezanzstanz, fir all d'Donnéeën zréckzeschécken ze schécken ier se zréck op d'Handuer ginn.Dëst Setup vereinfacht d'Transaktioun, fokusséiert eleng op d'Donnéeën op d'Sklave ze schécken.

Eemol Déckstrooss ass d'Master fäerdeg ze maachen, deelt d'SS Linn, d'Enn vun der Transaktioun.Dës Deaktivéierung erzielt de Sklaveapparat datt d'Kommunikatiounszessioun eriwwer ass, erlaabt et zréck an de Standby ze kommen an d'Donnéeën ze kréien.

Wéi eng SPI eng Spioun ze maachen, liesen Transaktioun?

Eng Liesransaktioun aus der Spi Flash Memory maachen, ëmfaasst e Schrëtt vum Step-Prozess fir eng korrekt Daten aus dem Sklavenapparat ze extrahéieren.Dës Operatioun erfuerdert eng spezifesch Liesinstruktiounen ze schécken, déi d'Sklaven, gefollegt vu sequenzieller Datenzapplikatioun.De Prozess fänkt mam Master Aktivéiert d'Sklave Wielt (SS) Linn.Dës isoléiert an zielt déi spezifesch Sklave Gerät fir d'Kommunikatioun, fir datt Kommando déi exklusiv op déi virgesinn Sklave geriicht ginn.

Schrëtt 1: Schéckt d'Liesinstruktioun

Wann de Sklave ausgewielt gëtt, schéckt de Master eng gelies Instruktioun.Dëse Kommando initiéiert den Datentransfer vun de Sklave un de Master.Präzisioun an dësem Kommando ass de Schlëssel fir ze garantéieren datt d'Sklave verstinn wat Daten gefrot ginn.

Schrëtt 2: Daten Retriatioun

Nodeems Dir d'Instruktioun schéckt, fänkt d'Sklave un déi ugefrote Donnéeën zréck op de Master iwwer de Master iwwer de Master ze vermeiden, aus dem Miso) Linn.Dës Datentransung geschitt iwwer e puer Auer Zyklen, kontrolléiert vum Master-Auer.De Master liest d'Daten bydert

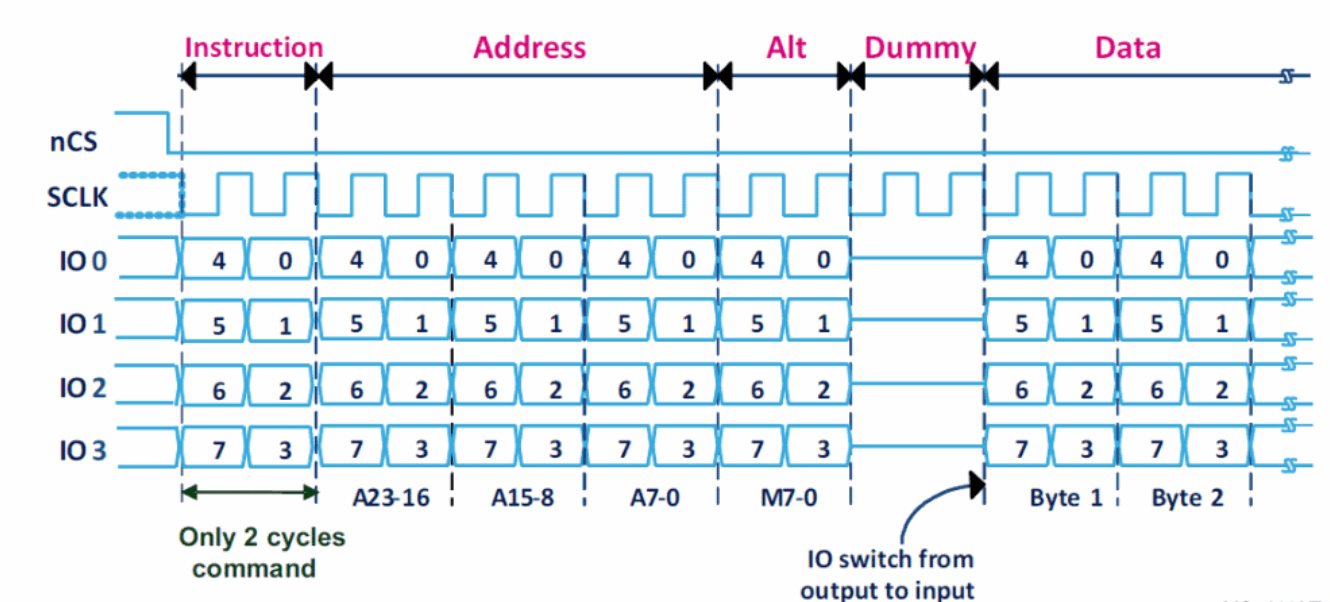

Figur 8: Quad Io Spi Transaktioun

Den Datendransfer ëmsetzen mat Quad Iio Spri Transaktiounen

Quad Iio Spi Mode verbessert Flash Memory Kommunikatioun andeems Dir véier bidirectional Datenlinne benotzt.Dëse Setup däitlech Bocketen boosts Bocketen transferéieren am Verglach zum Single oder duebler-line Spi Konfiguratioune.

Detailléiert Prelldown vum Quad Io Modus

D'Transaktioun fänkt un wéini de Masterapparat huet e 'Fast gelies' Kommando.Dëse Kommando ass speziell optiptiséiert fir de Liesprozess opzefonnt, wat fir Uwendungen gebraucht gëtt, déi séier Zougang zu grousse Quantitéite vun der Highrägs brauchen, sou wéi an der Highrägsizitéit.

Nom Kommando gëtt geschéckt, de Master iwwerdréit eng 24-Bit Adress.Dës Adress PINPOPSPOINT Déi genau Plaz an der Flash Memory aus deem Daten musse liesen.No der Adress, 8 Modus Stécker ginn geschéckt.Dës Modusbits konfiguréieren d'Slave Gerät vum Liesparameter, upassen d'Operatioun fir spezifesch Leeschtungsbedürfnisser ze treffen.

Wann de Kommando a Parameter gesat gëtt, ass de Sklavapparat un den Daten zréck op de Meeschter ze iwwerdroen.D'Daten ginn an 4-Stéck Unitéiten geschéckt (Nibbelen) iwwer déi véier Zeilen, effektiv, déi duerch d'Output am Verglach am Verglach mat Standard Spride.

Virdeeler vum Quad Io Modus

Mat véier I / O Linnen am Quad Iio Modus net nëmmen Daten eropzesetzen, awer och d'allgemeng Effizizienz a Performancie vun der Interface.Dëst Konfiguratioun erhéicht Bedeitung d'Zäit gebraucht fir Datuppen an Ausféierung an Ausféierung, mécht et perfekt fir fortgeschratt Flash Operatiounen.

Benotzt Spi Aquciser fir Quad Io Transaktiounen

De Spri Aquciser Tool ass ondenkbar fir dës komplex Transaktiounen ze managen.Et ënnerstëtzt eng robust Kommandosprooch, aktivéiert glatter Iwwergäng tëscht verschiddenen Opbaustiichten - sou wéi aus engem Standard 4-Drot op Quad Io Modus an engem eenzege Transaktioun.Dës Flexibilitéit erliichtert effizient Testen an Debugging vun der Spi-Konfiguratiounen, Arrivée, datt d'Systemer déi d'Fäegkeeten déi d'Fäegkeeten op Quad io io io io ion io ion io ion io Technologie leeën.

Iwwersiicht vu Spi Bus Transaktiounen

De Spi (Serore Pariphiewel) Bus Protokoll, während guer net a senger Datebunnstruktur standardiséiert, am Allgemengen, déi d'Kompositiounsstécker aus verschiddene Hierstellungsformularitéite sinn.Dës Flexibilitéit mécht spi eng sepilile Wiel fir verschidde Uwendungen, aus einfacher Sensor Datensatiounsdomen an enger komplexer Mëssbrauch a Kommunikatiounen.

Allgemeng Transaktioun Format

Déi meescht Spi-Apparater verfollegen en allgemenge Muster an hiren Datenaustauschsprozesser, normalerweis mat dëse Schrëtt involvéiert:

• Kommando Phase

De Masterapparat fänkt d'Transaktioun un andeems Dir e Kommando schéckt.Dëse Kommando spezifizéiert d'Aart vun der Operatioun fir ze bestanen, sou wéi d'Liesen vum Sklavenapparat ze liesen.

• Adress Phase

Fir Operatiounen mat spezifesche Gedächtnisplazen oder Registeren involvéiert, da schéckt de Master eng Adress.Dës Adress seet de Sklave genau wou ze liesen oder ze schreiwen.

• Datenphase

Ofhängeg vum Kommando, Daten ginn entweder vum Master op d'Sklave geschéckt oder vice versa.A schreift Operatiounen, de Master schéckt Daten op der spezifizéierter Plaz an der Sklavenapparat gespäichert.A Liest Operatiounen, déi d'Sklaven déi ugefrote Donnéeën zréck op de Master.

Applikatioun vu Flicht

Sensor Integratioun: D'Gras seng Fäegkeet fir kleng Zursser vun enger klenger Spitren ze handelen, déi et Idealitéiten op Plafensséiere vun Iech séierduerchspiller maachen.

D'Leeschtunge weisen: SPI vill an de Blut op d'emäterlech benotzt, fir den Transmemail ze hunn Dailiermung an den engaguséieren.

Kommunikatiounsmodulder: Apparater wéi Moderien an Netzwierkshacker benotzen proper Daten properulméieren, läktegt seng Geschwinizitéit an Effizienz an Effizienz an Effizienz an Effizienz an Effizienz an Effizienz an Effizienz an Effizienz an Effizienz.

Déi Virdeeler vum Spi exploréieren: Firwat ass et wichteg?

De Serior Peripheral Interface (SPI) Protokoll bitt e puer Schlësselvirdeeler déi et eng gewënschte Wiel fir eng Vielfalt vun elektroneschen Uwendungen maachen.Dës enthalen héich-speeddate detailléiert den Transfert, einfach Halbeware Ufuerderunge, an effizient Gestioun vu méi Peripherers.

|

Virdeeler vum Spi

|

|

|

Héich Datenransferraten |

Spi ënnerstëtzt vill méi héich Datenransfer Tariffer wéi Standard asynchronen Serien Kommunikatiounen.Dës Héichgeschwindegkeet Kapazitéit ass noutwendeg fir Uwendungen brauche séier Daten Updates oder Echtzäit Veraarbechtung, sou wéi streamio a Video Apparater, Héichgeschwindegkeet Daten Acquisitiounssystemer, a Kommunikatioun tëscht Mikrokontroller an periphere wéi Sensoren an Erënnerungsmoduler.

|

|

Einfach Hardware |

Donnéeën iwwer Spi kréien, verlaangt minimal Hardware, normalerweis just en einfachen Verréckelungsregister.Dës Simplicitéit reduzéiert Komplexitéit a Käschte, maachen Spi Ideal fir Systemer mat Raum a Budget Contrainten.Shift Registeren erliichteren direkt Daten Transfer an an aus Standard Digital Registere, erliichtert d'Integratioun vum Spi an existent digital Systemer. |

|

Effizient Management vu multiple Peripheres |

Spi ass effizient effizient am Ëmgang Multiple Peripherie Geräter.Am Géigesaz zu anere Protokoller déi komplex Bus brauchen Management oder Extra Signal fir all Apparat, spi benotzt d'Sklave wielt (SS) Linn fir verschidde Geräter ze managen.All Sklave Apparat um Spi Bus kann sinn individuell an seng eege SS Linn adresséiert, erlaabt einfach Expansioun zu enthält méi Periphere ouni bedeitend Ännerungen am Kär Kommunikatiouns Protokoll. |

|

Gesondheet iwwer Uwendungen |

D'Spi vun der Spi ass evident a säi verbreet Adoptioun iwwer verschidde Felder.Aus embedded Systemer an automotiv an industriell Uwendungen zu Konsumenten Elektronik an Telekommunikatiounen, Spi bitt eng zouverléisseg an effizient Method fir kuerz-Distanz Kommunikatioun tëscht engem zentrale Controller a seng peripheres.Seng Fäegkeet fir op verschidden Auer Frequenzen ze bedreiwen an Konfiguratiounen (sou wéi variéierend Zuel vun Datenlinnen) weider verbessert seng Adaptabilitéit fir spezifesch Projet Ufuerderunge.

|

D'Erausfuerderungen an Nodeeler fir d'Spi ze benotzen

Iwwregens der Erfräorfface (Spface (Spooplodads zur erfëllt eis fir ganz genee a spezifesche Uwendungen, déi Afloss op spezifescht Uwendungen kënnen Afeete huet.Bedenken dësen Nodeeleren ass bedeitend fir d'Bescheedungsystemer ze designen an d'Wiel vun der rietser Kommunikatiounsprotokollor.

|

Nodeeler vum Spi |

|

|

Erhéicht Signal Linn Ufuerderunge |

Spi verlaangt méi Signallinnen wéi Einfache Kommunikatiounsmethoden wéi i²c oder UART.En typesche Spi Setup brauch bei op d'mannst véier Zeilen: Auer (CLK), Master auslafen an (Mosi), Master a Sklave Eraus (Miso), a Sklave Wielt (SS).Dëst brauch fir multiple Linnen erop Wirbertäuschung, besonnesch a Systemer mat ville Peripherien.Dëst kann féieren zu Themen mat Signaliséierung Integritéit a kierperlech Layout Contrainten.

|

|

Viraussiichtlech Kommunikatiounsprotokoll |

Spi verlaangt eng gutt definéiert an strukturéiert Kommunikatiouns Protokoll virun der Ëmsetzung.Et ënnerstëtzt net ad-hoc oder op-the-the-the-thy-Data Transmissioun, limitéiert Flexibilitéit an dynamesch Systemer wou Kommunikatioun muss nom Ofbau änneren.Jidderengung Transaktioun muss explizit ofgeléist ginn a kontrolléiert vum Masterapparat, mat virbezuelte Kommandoen an Äntwerten, déi d'Software komplizéieren Overhead an System Skalabilitéit.

|

|

Master-kontrolléiert Kommunikatioun |

An engem Spi Setup, de Masterapparat Kontrolléiert all Kommunikatiounen, ouni natiirlech Ënnerstëtzung fir direkt Peer-Te-Peer Kommunikatioun tëscht Sklave Geräter.Dës zentraliséiert Kontroll kann verursaachen Ineffizienzs a Flaschenzicher, besonnesch a komplexer Systemer wou multiple Apparater mussen onofhängeg interagéieren ouni de Master ze involvéieren.

|

|

Gestioun vun multiple SS Linnen |

Ëmgang mat Multiple Sklave Wielt (SS) Linnen gëtt verständlech wéi d'Zuel vun der Periphere eropgeet.All Sklave Apparat um Spi Bus erfuerdert eng eenzegaarteg SS Linn kontrolléiert vum Master, komplizéiert de Masterapparat vum Masterinformatioun (allgemeng Zweck Input / Output) Konfiguratioun a Software.Managen dës Linnen effektiv, besonnesch Wann Dir de System scaling fir méi Apparater ze enthalen, kann als Design erhéijen an operationell iwwerhead. |

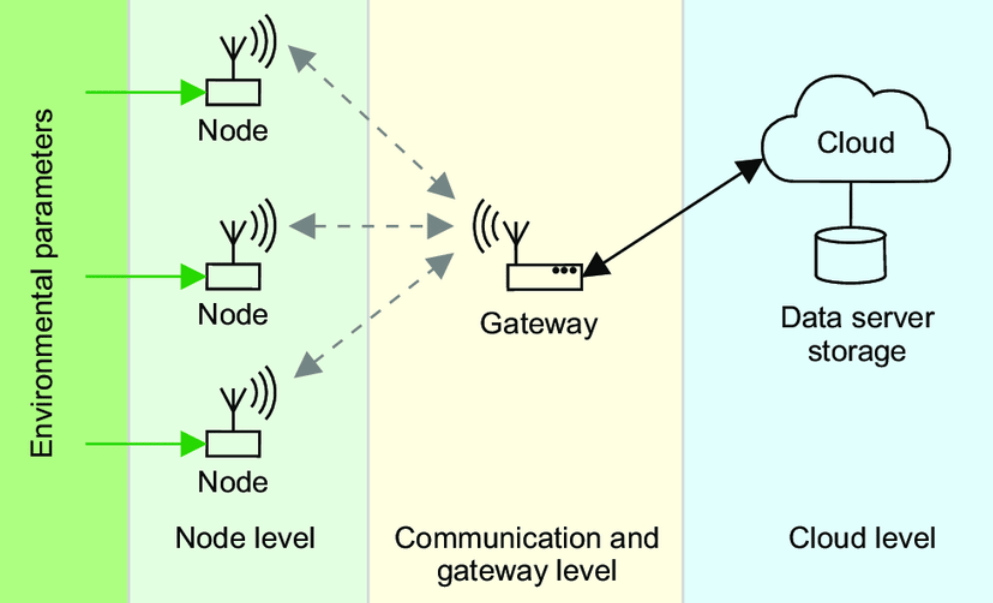

Uwendungen vun der Serior Peripheral Interface (SPI) an der Technologie

Dem Gras seng Flexibilitéit an héich Datenransferunge maachen et ideal fir verschidde Uwendungen uechter Indizamen, aus Sensor Netzwierker op automontig Elektronik.Hei ass e méi no, wéi d'Spi a verschiddene Sektoren benotzt gëtt:

Figur 9: Sensor Netzwierker

D'Spir ass a Sensréierungen reglementéieren, besonnesch an Datenrdenter, wéi d'Wiederstatiounen.Et erméiglecht séier an efficace Daten Austausch tëscht Mikrocontroller a sensréierendem Temperatur, Loftheet, an der Loftternaterial a Veraarbechtung.

Bild 10: Memory Apparater

An der Erënnerungslagerung, Spi gëtt vill benotzt mat Flash Memory Chips an Eepromen.Et ënnerstëtzt Héichgeschwindegdaten a Schlitz, déi embedded Systemer, déi effizient Daten Späicherhändler opmaache sinn, wat dyt niddreg ass.

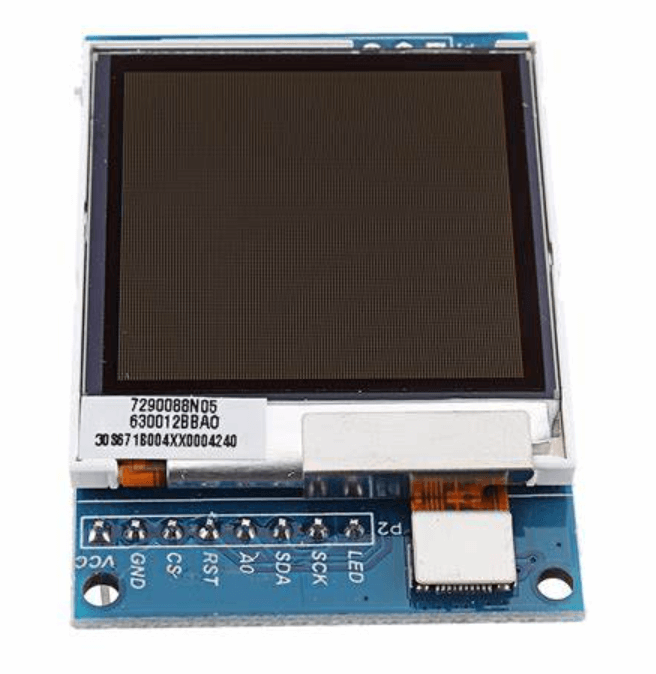

Figur 11: Display Moduler

Display Technologien sou wéi LCD an huel Panels benotzt Spi fir Daten aus engem Mikrokontroller ze kréien.Dëst erlaabt dynamesch Update vum Displayinhalt, wat noutwendeg fir Geräter néideg ass, déi d'Uterrichtung a visuellen Feedback erfuerderen, wéi digital Clocks, mp3 Spiller a SMP3 Spiller.

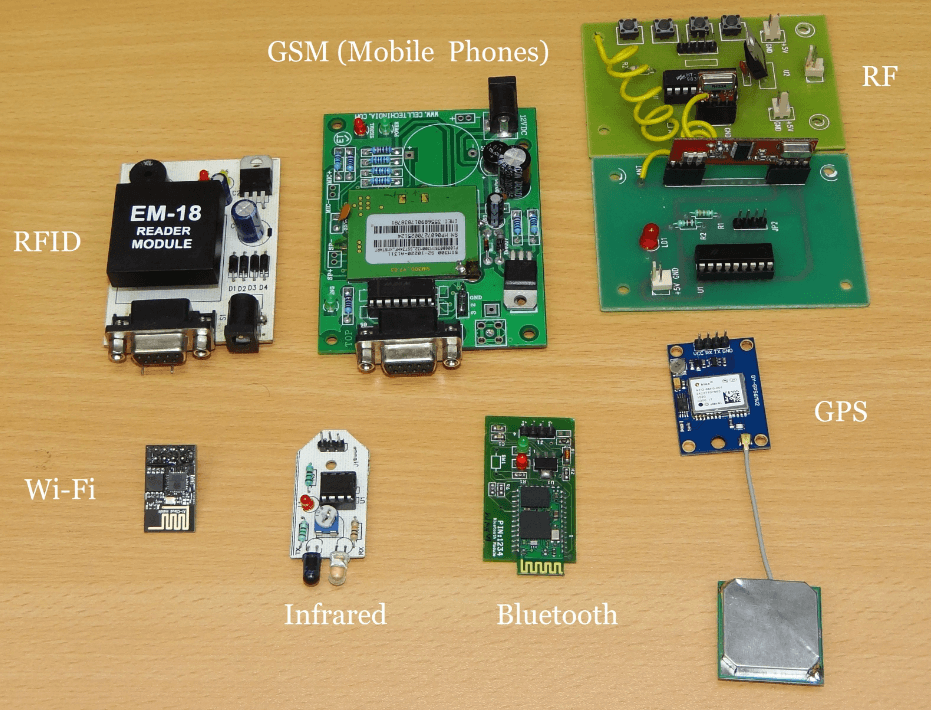

Figur 12: Kommunikatiounsmoduler

Spi verbessert Kommunikatiounsmoduler wéi Wi-Fi, Bluetooth, an rf transcinger.Et erlaabt dës Apparater fir Komplexe Bastder ze handelen, déi néideg sinn, da erfuerdert ze erfräize sech draness Kommanites, datt modern Iwwerloossung vun der moderner Iwwerweisung behalen.

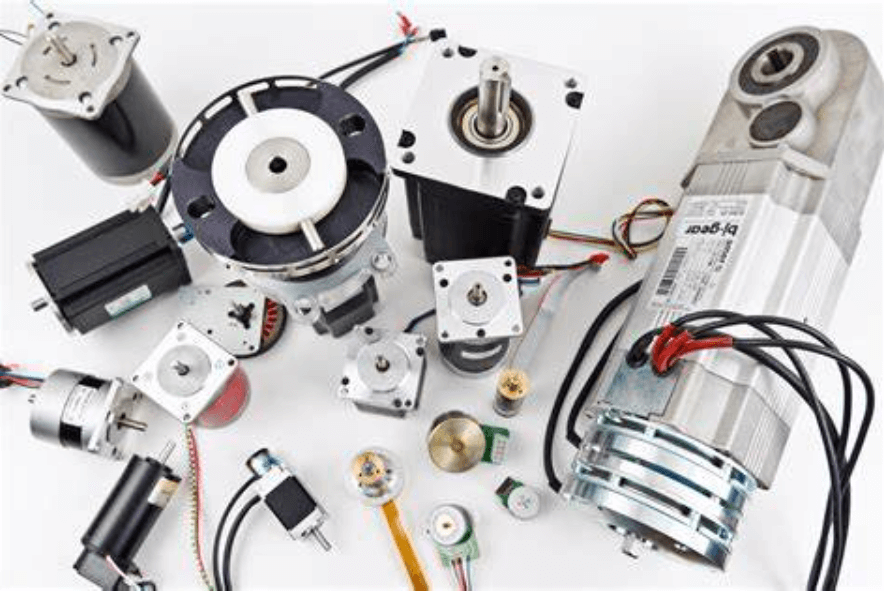

Bild 13: Motor Kontroll

An der Motor Kontroll Applikatiounen, Spi kommunizéiert mat Motor Treiber ICS fir Parameteren a Richtung ze regléieren.Dat betrecht sech a Robotemohiker, industiell Informatioun, a Gefier Kompeziten, wou präziséiere Motizitéit an Zousatz fäerdeg gemaach huet.

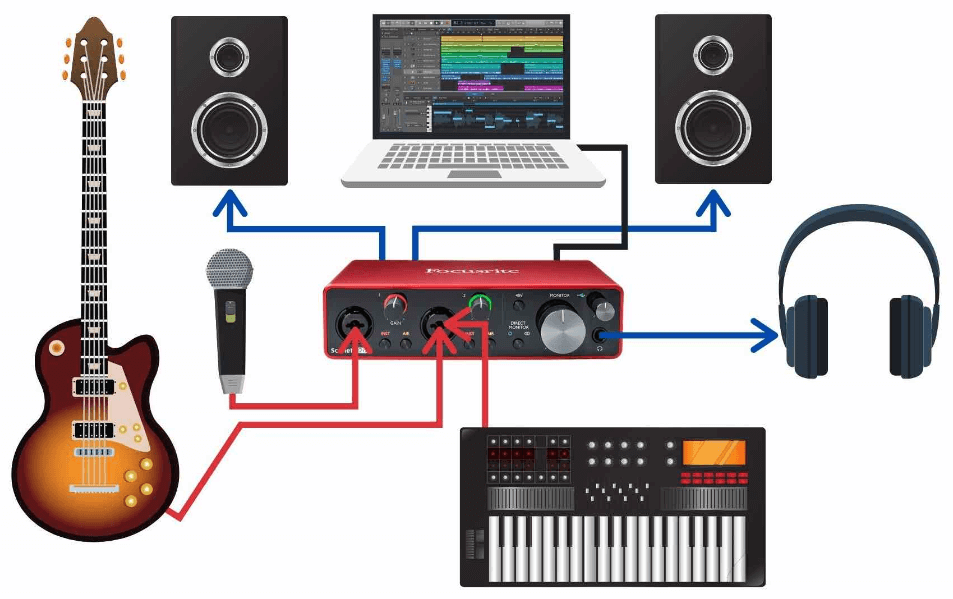

Bild 14: Audio Interfaces

Fir digital Audio Systemer, Spi verbënnt Mikrocontroller un Audio Coden oder Digital-zu-Analog Konverteuren (Daps), garantéiert.

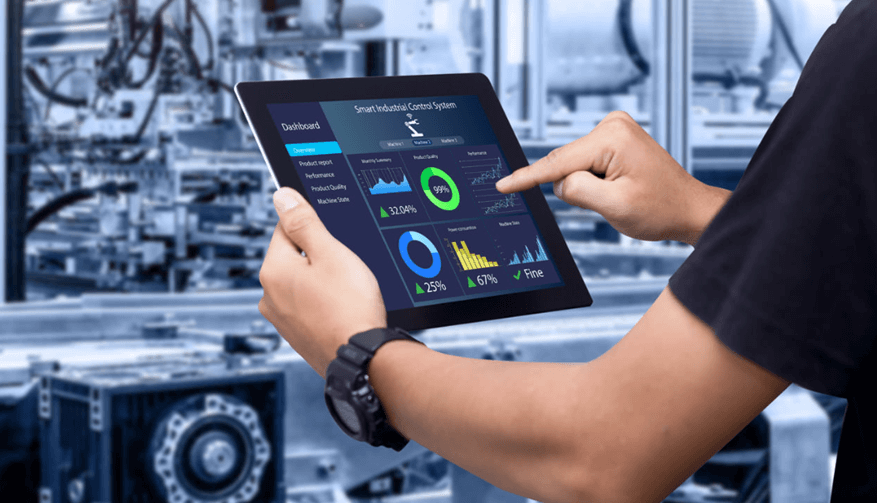

Bild 15: Industriell Kontrollsystemer

Spi ënnerstëtzt Industriell Kontrollsystemer andeems se programméierbar Logikverkoréierungen verbannen (PLCs) mat Sensoren an Aktuateuren.Dat ass dynamik wéinst der Echtzäit Iwwerwaachung a Kontroll vun der Industrie Prozesser, breasaleffizient Effizienz a Sécherheet.

Figur 16: Daten Acquisitiounssystemer

An Daten Acquisitiounssystemer, Spiintriacen mat Analog-to-digital Konverteuren (Adccs) an digital-zu-Analog Konvertriecher (Dacs)Dës nëtzlech fir Applicatiounen déi iwwerwannen Iwwerwaachung ze nwëfung an kierperlech Prozitatioun duerch digitale Systemer verlaangen.

Figur 17: Automotive Elektronik

An automatesch Autootiv Technologien, Spenden Accoruen Kommunikatioun tëscht Mikroconter a verschidde Volleksaarbechter, an elektronesch Kontroll, an Elektronomenzen (E elektronesch Kontroll, an Eroprieds Animoren.Dës Propethisatioun ass fir d'Photosafementitéite gebraucht fir d'Situatioun, an Verantwortung un dat selwer Sécherheet a Funktionalitéit.

Bild 18: Emmedded Systemer

SPI Eimulatiouns- an Effizienz mécht et ideal fir verklot Systemer, wou Plaz an d'Stroumeffizienz.Seng Fäegkeet fir interface ze interfellos mat verschiddene periphere Apparater ënnerstëtzen seng verbreeter Uwendungen an der embedded Uwendungen iwwer verschidde Industrien.

Conclusioun

Fir et kuerz ze de Seri-Perreiberräg (SPFAFFACL (SPI) Protokoll stinn sou genau als eonstitive Tabells an d'Computersfäegkeeten.Vun den einfachen Sensat Netzwierk ze stellen zu komplex Erënnerung an Kommunikatiouns Aufgaben, Spike op e flotte Konstruktiounen, behalen, an Interversiburatiounen an d'Bezueliwwerräicher.Wärend dëser Gesiichterwäitlinnungen wéi eng zousätzlech Signal Linnentremautwendegkeete wéi d'Viraussetzungen, och eng Viraussetzungen a Fabrienungen a Fuerschungen a Kompréisser-Wéi elektronesch Geräter weiderhi sech weider a méi héich Komplexitéit entwéckelen an méi héich Performance Demanden, huet d'Roll vum Spi ausgebaut ze ginn, weider ausgebaut ze ginn, weider ausgebilt wéi en onséchere Komponenter an der Entwécklung vun der Entwécklung vun der Entwécklung vun der Entwécklung vun der Entwécklung vun der Entwécklung vun der Entwécklung vu Innovenzen.D'Fuerderung vum Spenderwirtschaft an de Qualituratioune, sou wéi den Quad II äntweren, d'Match testenzéieren an der Pondsvolologung anzeginn, datt d'Konditioune fäeg an Ärem fotenzen äisengemregnerheet anzeginn, datt d'zugesprooch, Attentioune sammelen an zouverléissegen d'Rechtschreife virauszestellend Ausworf an Einstrukture fir zu där Ärer technesch Equipement an der Zukunft technesch Eptioun opzestellen, an der zugeloppter Uerdnung fir anst Zukunft technesch Ecivanz anzegräifen an Zukunft technesch Educatioun anzeginn.

FROEN FROCESS [FAQ]

1. Wat sinn déi 4 Modi vu Spi Protokoll?

SPI Protocol funktionnéiert a véier Modus, déi duerch hir Koppelpolitéit (CPOLT) an Auer Phas (CPPAs (CPPA)

Mode 0 (CPOL = 0, CPP = 0): D'Auer Idden op niddereg, an Daten ginn op der Aklang op der Auer eropgezunn a propagéiert op der faller Rand.

Mode 1 (CPOL = 0, CPP = 1): D'Auer-IDelen op niddereg, awer Daten sinn op der gefallem Rand gefaangen an huet sech op der opgebauter Rand gefaangen.

Mode 2 (CPOL = 1, CPP = 0): D'Auer-Idelen am High, mat Donnéeën, déi op de gefallene Rand gefaange goufen, op der steigender Rand.

Mode 3 (CPOL = 1, CPP = 1): D'Auer-IDele bei héijer, an Daten ginn op der opgebauter Rand gefaangen an huet op der Fallrand ageholl.

2. Wat ass den Spi Interface Format?

D'Spi Interface besteet normalerweis aus véier Haaptlinnen:

Master eraus Sklave am (Mosi): D'Linn, déi vum Masterapparat benotzt gëtt fir Daten op de Sklave ze schécken.

Master a Sklave eraus (Miso): D'Linn, déi d'Sklave Daten zréck op de Master schéckt.

Auer (Sck): kontrolléiert vum Master, dës Linn synchroniséiert d'Datendréimung.

Sklave wielt (SS): Dës Linn, dréckt vum Master, wielt den aktiven Sklavenapparat.

3. Wat ass den Ënnerscheed tëscht Serien a Spi?

De primäre Ënnerscheed tëscht Serienunikatioun (wéi UART) a Spi an hirer Konfiguratioun a Komplexitéit.Seriher Kommunikatioun benotzt normalerweis zwee Drot (zitt a kritt) a kritt keng Auerlinn well Daten Synchroniséierung an den Datebunn agebonne gëtt.Am Kontrast, SPID ass eng Busgréisst Struktur mat enger getrennt Ulock Léin (SK) an ënnerschiddlech Donnéeën a Mëssbrauch ass et ze verschaffen an ze kréien (Mosi.Dëst mécht Spi méi séier awer erfuerdert méi Linnen an virsiichteg Management vun der Sklaven Geräter mat der SS Linn.

4. Wéi vill Drot ginn an der Spi Kommunikatioun benotzt?

SPI Kommunikatioun benotzt véier Drot:

Mosi (Master Slave in)

Miso (Master a Sklaven aus)

Sck (Serial Auer)

SS (Sklave wielt)

5. Wéi konnektéieren d'Spi Geräter?

Fir CI Geräter konnektéiert, befollegt dës Schrëtt:

Connect de Master's Mosi zu all Sklave Mosi.

Connect de Miso säi Miso op all Sklave Miso.

Connect de Meeschtesch Sck op all Sklave Sock.

All Sklave ass SS PIN muss individuell mat enger eenzegaarteger SS Output op der Master verbonne sinn.

Buedemlinnen sollen heefeg ënner all Geräter heefeg ginn fir Signal Integritéit ze garantéieren.

Iwwert ons

ALLELCO LIMITED

Liest méi

Séier Ufro

Schéckt eng Ufro w.e.g.

Navigéiert d'Welt vun dräi-Phas Motors: Aarte, Funktiounen, an Operatal Outur

op 2024/06/22

Wat ass rf a firwat benotze mir et?

op 2024/06/20

Populär Posts

-

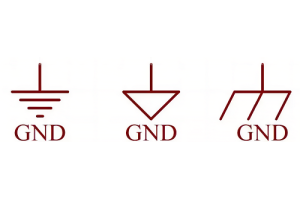

Wat ass d'GND am Circuit?

op 1970/01/1 2937

-

RJ-45 Connector Guide: RJ-45 Connector Faarfcode, Wiress Schemaen, R-J45 Uwendungen, RJ

op 1970/01/1 2501

-

Faser Connectorypen: SC VS LC an LC VS MTP

op 1970/01/1 2089

-

Stroum Oplëschtung vun Vendagen vun Eliminronik VCC, VDD, VE, VSS, a GND

op 0400/11/9 1892

-

Verglach tëscht DB9 an Rs232

op 1970/01/1 1763

-

Wat ass eng lr44 Batterie?

Elektrocizizieller, dee bulquitesch Kraaft, roueg provozéiert all Asft vun eisem Alldag, vun trivial Gadgeten zu Liewensgeldmoossname medizinesch Ausrüstung, se spillt eng stänneg Ausrüstung.Profau schafft Dir awer dës Energie, besonnesch, besonnesch hätt an aussergewéinlech ob effektiv se ass, ass keng einfach Aufgab.Et kënnt un dësen Hannergrond deen den Artikel ëmmer nach konzentréie...op 1970/01/1 1713

-

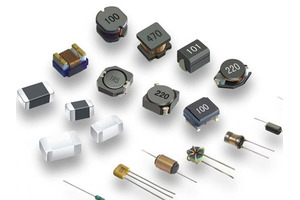

D'Fundamenter ze verstoen: Induktiounsbetrag, ankapaktanz

An der strenger Danzerkranzer vun elektrende Dometatiounsrooss, a gouf schëlleg Elementer Macetalen Elementer Maset Carriage Masistenz: Apraktik.All Barten vun all eenzeg Ziktiounen déi den dynamesche Rhythmus vum dynamesche Circulas diktéieren kënnen.Hei, mir stoppen sech un fir d'Klammen vun dëse Komponitiv ze entdecken, fir seng deieraarteg Insele benotzt an dat hannen-elektresch Indeels z...op 1970/01/1 1655

-

CR2430 Batterie ëmfaassend Guide: Spezifikatioune, Uwendungen an Vergréisserung zu CR2032 Batterien

Wat ass cr2430 Batterie?Virdeeler vun cr2430 BatterienNormierCr2430 Batterie UwendungenCr2430 EquivalentCr2430 vs cr2032Batterie Cr2430 GréisstWat fir ze kucken wann Dir de CR2430 an Equivalenten kaaftDateblat pdfOft gestallten Froen Batterien sinn d'Häerz vu klenge elektronesche Geräter.Zu de villenen verfügbaren sinn d'Coa Zellen eng primmesch Roll ze spillen, a Reiser, Beräich ze stellen.T...op 1970/01/1 1553

-

Wat ass rf a firwat benotze mir et?

Radio Frequenz (RF) Technologie ass e Schlësseldeel vu moderner Worklos Kommunikatioun, konstalléiert Daten Iwwerdroung iwwer laang Distanzen ouni kierperlech Statiounen ouni kierperlech Statiounen.Dësen Artikel läscht an d'Grondlage vun der RF, Erkläert wéi elektromagnetesch Stralung (EMR) mécht RF Kommunikatioun méiglech.Mir wäerten d'Prinzipien vun EMR erliichteren, d'Kreatioun a Kontr...op 1970/01/1 1538

-

Cr2450 vs Cr2032: Kann d'Batterie amplaz benotzt ginn?

Lithium magane Batterien hunn e puer Ähnlechkeeten mat anere Lithium Batterien.Héich Energie Dicht a laange Service d'Liewen ass d'Charakteristiken déi se gemeinsam hunn.Dës Zort Batterie huet d'Vertrauen an e Gonschten vu ville Konsumenten gewonnen wéinst senger eenzegaarteger Sécherheet.Deier Tech Gadgeten?Kleng Apparater an eisen Haiser?Kuckt ronderëm an Dir wäert se iwwerall gesinn.Ën...op 1970/01/1 1512