Mastering SR Latches: Symboler, Funktiounen, a praktesch Uwendungen

E SRLatch ass en asynchrone Circuit deen onofhängeg vun Auer Signaler funktionnéiert, mécht et e villsäitegen Tool an verschidden Uwendungen.Et hält e binärer Staat- entweder héich (1) oder niddereg (0)-anstatt eng eenzeg Quantitéit, déi et hält, bis nei Inpute Signaler eng Ännerung.Dëse Basis Binäre Späicherelement ass gebaut mat zwee cross-gekoppelt Logik Gates, typesch an nan Gates.De Set Input (en) aktivéiert d'Latch, an den Ausgang (q) ze héich op héijer, wärend de Reset Input (r) setzt den Ausgab op niddereg.D'sinn awer allflächegall héich Signalerelen déi béid Infirmen enthalen op e befestegte Memberstverstand fektionnéiert.SR Latch sinn net nëmmen theoretesch Konstruktiounen;Si goufen an der praktescher Systemer implementéiert fir temporär Daten ze halen, ënnerstëtzt Provenatesch-Resultater, an och Feeler Feeler an Kritesche Geräter an de medizinente Apparater.Calalog

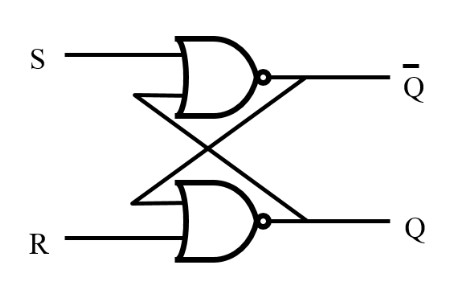

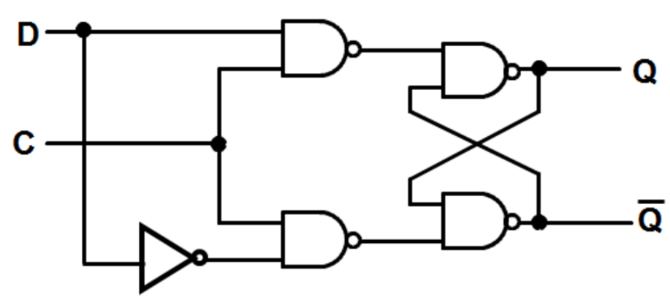

Bild 1: SR Latch

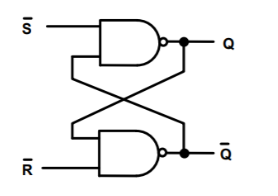

Wat ass en SR Latch?

E SRPLatch, oder Set-Reset-Reset Latch, ass eng Basis Binärzenter Element dat zu der Kategorie vu Asynchron Circuits gehéiert.Am Géigesaz zu Synchrone Circuiten, SR Lavards fuerdert ouni Knock Signal, erëm eleng op den direkten Kontrollvignaler nei ze bedreiwen.Dëst erlaut dënn net immens eigentlech am Digital Fighit.En SR Latch kann zwee stabile Staaten erhalen: héich (1) an niddereg (0), aktivéiert en eenzegen Informatioun ze späicheren bis vun neie Input Signaler.

En srlat latch implizéiert normalerweis zwee keegentologesch Logikpatten, allgemeng nach Gata oder Nandpata.An engem sr latch Design mat Hëllef vun net Gates, den Ausgang vun all Gate verbonne mam Input vun deem aneren, bilden eng Feedback loop.Dës Konfiguratioun ass garantéiert datt de Latch net verännert Staat baséiert op der Input Signaler beim Erhalen, déi d'Stabilitéit erhalen, bis en neien Input eng Ännerung.

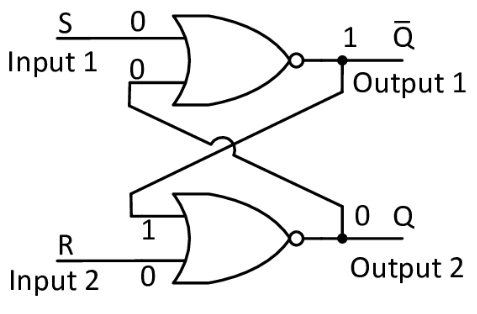

Figur 2: Sr latch (2)

Set Input (en): Wann de Set Input (en) ageschalt ass (héich), de Latch Ausgang (Q) Schalter op héich (1).

Reset Input (R): Wann de Reset Input (R) aktivéiert (héich) ass, den Ausgang (Q) Schalter op niddereg (0).

Wéi vill Inpsen héich: ob béid S a r Stapice am Viraussetzungsdauer geleet, gëtt de Etapparat an den Design verhellt sollt.

SR Last sinn essentiell fir temporär Datenlagerungen an Tëschestréierungsresultat behalen an digitalen Systemer.Si sinn déi fundamentativ Elementer a méi komplexe sequentiale Circuiten wéi Multi-Bit-Bit-Bit-Remiseren, Erënnerung Eenheeten, a bestëmmten Aarte vu Griewer.

An dësem Klinéeën komme SR de STRE Gäert, déi stabil Donnéeën bidden, konnten séier op Ännerunge vun der exterustronescher System z'ënnerfallë ginn, garantéiert déi effizienter Signal vum ganze Signal vum komplette Signalen

Eng aner Creditistesch Uwendung vum SR Lasthen ass a Feeler gedréit a Rorderic vu digitaler Circuit.Wéinst hirer Fäegkeet fir e stabile Staat ze halen, kënne se de System Status ännert a séier an e virgesinn sécherer Staat op en Anomalien z'entdecken.Dës Feature ass besonnesch wäertvoll an der Grenzheetssystemer wéi Aerospace a medizinesch Geräter.

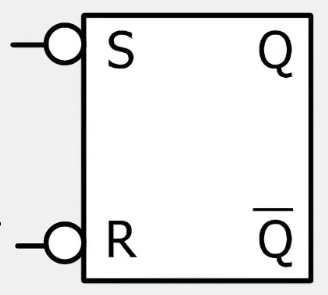

Symbol vum SR Latch

Säi Symbol an der Struktur ze verstoen ass fundamental fir seng Operatioun an praktesch Benotzung ze begräifen.A Circuit Diagrammer, de SR Latch huet normalerweis zwee Haapt Input Ports Label oder Set) a R (RESET).Dës Inpute kontrolléieren d'Output vum Latch vum Latch vum Latch vum Latch, dee selbst representéiert als Q. E puer Motiver funktionnéiert och den inverse Output, deen q '"huet, wat de Géigendeel Zoustand gëtt

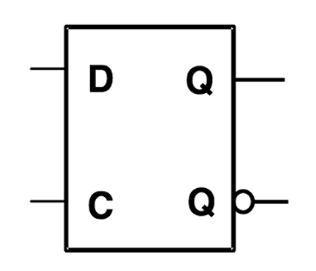

Figur 3: Symbol vum SR Latch

Als SR System gëtt dacks mat engem redänglechen Symbol mat Inpen vertruede mat Inputen s an emol eng Ausgab Q 'astnesch erechen.Dësen CC Tclement kënnt d'Circuit d'Funktiounen fir séier ze identifizéieren an seng Roll am Kallati.

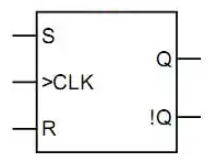

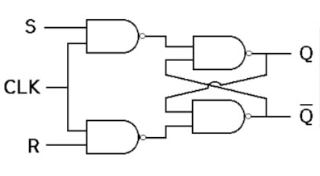

Eng gemeinsam Variant vum SR Latch enthält eng Auer (CLK) Input.De CLK Input ass garantéiert datt d'Staat Ännerungen am Synchc mat der Auer Signal passt, eng präzis Timing Kontroll kréien.An dësem Setup, och wann s oder r ageschalt ass, ass de State vum Latch aktualiséiert wann de CLK Signalpositiounen spezifesch Konditioune entsprécht, gëtt normalerweis op der opgaanger oder falen.Dëst verhënnert datt Feeler duerch Input Signal Glitches oder onbedéngt Ännerunge verursaacht goufen.

Figur 4: Symbol vun der Auer-gated Sr Latch

De gekloote SR-Symbol-Symbol enthält d'S, R, a CLK Input an engem Rechteck.Dës stetionnant Regdung hëlleft d'Situatioun vun de Funktionalitéit ze verstoen an säin Zeienkommen.Zum Beispill, an der Héich-Performance Computeren- oder komplex Datentdransfer Systemer, virsiichteg CKK Kontrollen déi d'Donnéeën op all Veraarbechtung vun all Veraarbechtung vun all Veraarbechtung vun all Veraarbechtung vun all Veraarbechtung vun all Veraarbechtung an der Rei sinn.

Genau Kontroll vun der SR Latch Input ass wichteg, besonnesch am Design vun héijer Geschwindegkeet an eng grouss Kapazitéitszorder oder temporär Datenbufferen.Andeems Dir logesch Circuits manifestéiert fir S an R Aktivéierung ze managen, komplex Funktiounen wéi Dateblieder, Clearing, oder Staat Resetting kann erreecht ginn.A korrekt kkk Signal Kontroll garantéiert datt all Daten Operatiounen eng preefed Timing Timing Sequenze follegt, bedingt d'Systemereffizienz- an Datenveraarbechtungsfäegkeet.

En déiwen Verständnis vum SRGLATS Symbol an Struktur Aids net nëmmen am korrekten Circuit Design an Troubleshooting, awer och an der Coud Callital Callic Callic Callic Operations a verbessertDëst ass besonnesch kritesch an Demeweitungsinformatiounen anform an eng präzis Kontroll, sou wéi Aeracace an medizinesch Geräckung.

Aarte vu Latches an hir Aarbechtsziegelen

Breete ginn fundamentéiert Komponenten an elektronesch Design, proposéiert d'Divers Funktiounen a breet Uwendungen bidden.Den Haapttene vu Latzer sinn SR deelen an ze Linnen, kënnen all mat eenzegen Operatiounen an ausfalen.

Sr latch

DEN SRLSCHALL, ODER SET-RESET LOGAT, ass e Basis Späicherapparat kontrolléiert duerch seng zwee Input, S (Set) an R (RESS).

Wann de s Input en héije Signal kritt, gëtt d'Ausgab Q héich, wat d'Donnéeën uginn ass.Wann de R Input en héije Signal kritt, gëtt den Output Q niddereg, wat d'Donnéeën zréckgesat gëtt.Wa béid S an r Inpute héich gläichzäiteg ënnersträichen, erot d'Demit vun engem ondefinéierte Staat, verursaacht potenziell Ustrengung.Dës Conditioun muss am Design ofgedeelt ginn.D'SR Latch ass direkt Äntwert op Input Signaler mécht et nëtzlech an de Situatiounen déi séier Reaktioun erfuerdert.

D latch

D'OLatch, och bekannt als Datapparat oder opdréitLSCHRE-System, bitt méi komplex Kontroll mat den Dateninformal Klin

Figur 5: D Latch

Figur 6: D latch Symbol

Wann de Click héich ass, the Output q follegt den Input D, erlaabt d'Donnéeën duerch d'Latch fräi ze passéieren.Wann de k kascht sinn, den aktuelle Wäert vum D ass gespaart an d'Outpaft q konstante bis op de nächste ksant.Dëse Mechanismus mécht den D Latch ideal fir temporär ze späicheren Daten fir verschidden Veraarbechtungsgeschwindegkeeten an engem System ze synchroniséieren.

Sr an D Latches hunn eng onparörelléiert Roll an der Dateschlager a Staat Machen Logik.Wéinst hirem direkten Input Niveau Äntwert, Latches sinn essentiell am Design als léif Circuiten.Si bidden déi vital Funktiounen fir ganz aktiv Verflëssungen an Stroummanagungsystemer, effektiv ze stéieren; stänneg Operatioun.EENZEN Notzung vun dësen Dolache kënnen zoustänneg Cuitculaibilitéits- Zouizzesser verbesseren, déi se net onkomplexiséierbar a moderner elektresch elektresch Selbstkontrakter maachen.

Wourecht Dësch vun engem SR LATCH

Bild 7: SR NAN LATCH

|

S |

R |

Q nous |

Q ' |

Notegéieren |

|

0 Boneier |

0 Boneier |

1 |

1 |

Verbueden |

|

0 Boneier |

1 |

1 |

0 Boneier |

Gesat |

|

1 |

0 Boneier |

0 Boneier |

1 |

Resréck |

|

1 |

1 |

Q nous |

Q ' |

Behalen |

CRANANCARL...ar 1: Wourecht Dësch vum SR Latch mat Nand Gates

Figur 8: SR Ownat

|

S |

R |

Q nous |

Q ' |

Notegéieren |

|

0 Boneier |

0 Boneier |

Q nous |

Q ' |

Behalen |

|

0 Boneier |

1 |

1 |

0 Boneier |

Resréck |

|

1 |

0 Boneier |

0 Boneier |

1 |

Gesat |

|

1 |

1 |

0 Boneier |

0 Boneier |

Verbueden |

CRANANCARL...ar 2: Wourecht Dësch vum SR Latch benotzt nach

NOT ECH OPZUELT DEM Wouresiturraum vum SR KOMMER NORMS BUST ASS ASS ASS BUSTATIOUN D'Bedeitung vun der Wourechtstand vum SR Latch ze verstoen.

Input an Ausgangsstatiounen

Béid s an r si 0: De Lizard bleift a sengem aktuellen Zoustand.Den Output q bleift d'selwecht, egal ob et 0 oder 1 ass.

S ass 0 an r ass 1: D'Latch resets, den Ausgangsk Q op 0 ze forcéieren.

S ass 1 an r ass 0: D'Latch Sets, d'Ausgab q gläich 1.

Béid s an r sinn 1: Dës Conditioun ass ongëlteg oder ënnerschratt ginn, bezeechent dacks als "verbueden" Staat an engem sr latch.Wat wierklech zäit goufen, Q an Q 'béid 0, féieren zu en brennege Queluss.

Wann s an r souwuel 0, den Hiwwel mécht näischt an hält säin aktuelle Wäert.Dëst ass nëtzlech fir de Staat ze halen ouni Ännerungen.

Wann s 0 ass an r 1 ass, ass de Latch explizit gesot, datt et zréckgesat gëtt ze goen datt de Q onofhängeg vu sengem fréiere Staat ass.Dëst ass e méi einfache Wee fir d'Latch ze läschen.

Wann s 1. an r ass de Latch ass agestallt, garantéiert Q gëtt 1. Dëst ass wéi Dir e '1' an der Latch stamt.

Si ass s an r eng zwee 1, de Staat dë si erlaabt well et déi béid Ausrieder sech am 0, wéi eng widerbar ass.D'Desuristers mussen dës Konditioun vermeiden fir stäckeg Operatioun ze garantéieren.

Virdeeler an Nodeeler vun de Latches

D'Lich ginn meeschtens am Digital Kital vun der Zieuladise benotzt wéinst hirer Einfachheet an niddregeets.Dës Charakteristike aktivéieren Lawchen op héijer Geschwindegkeete mat owespromement ze schaffen,, déi se ideal fir héichgeschniddene Digitatsmaterialsystemer maachen.Sou ass zum Beispill op de Gondspektiv behënnere komplett, d'Legisten kéinten e séier aechns, dun och d'Veraarbechtungssaktiounswarkt an Effizienz a Koordizes.

Virdeeler vun de Latches

Einfachheet a Käschte-Effektivitéit: Latches si riicht Komponenten déi gräift op digital Circuiten ëmzesetzen.

No grousser Voix an niddreg Kraaft: Hiert Design erlaabt séier Operatioun mat malime Kraaft, wat kritesch digiture proiguéiert kann.

Effung vun den Datenhandlung: Op Betrag u Kontributiounen wéi Prozessor registréieren d'Dateie, déi séier Donnéeën ofschléissen, a Retrementvall, Beruffsauszankternuecht.

Nodeeler vun de Latches

Trotz hir Virdeeler verstinn déi natierlech kengegdrounge bei verschiddenen Designen a Uferen unzeechnen.

Onberechenbar Verhalen an Asynchronous Designen: ouni Auer Signal Kontroll, Latches kënnen onberechenbar sinn.An SR Latchelen, wa béid (en) a reset (R) Inpute sinn héich gläichzäiteg, déi den Output ass, da féiert un Onstabilitéit.Dëst ass problematesch an Echtzäitkontrolle oder Sécherheet-kritesch Uwendungen, wou zouverlässeg Ausgab ass entscheedend.

Komplex Timing Design: Designen mat Latches erfuerdert virsiichteg Timender.Ingenieuren muss de Kont fir Signal Propagatiounspersonnagen a Rass Konditioune vermeiden fir den Timing Feeler ze vermeiden.Onméiglechkeeten Design kann zu Daten ännert sech virun der Auer Signal stabiliséiert, verursaacht Daten Korruptioun oder falsch Datencaase.Dëst brauch en déiwe Verständnis vun der timing Analyse a kreesfërmeg Verhalen.

Fir dës Erausfuerderungen ze adresséieren, spezifesch Designstechniken a Strategien kënnen agestallt ginn:

Synchroniséierungsmechanismen: Füügt Synchroniséierung Mechanismen kënne hëllefen Asynchronen Inputen ze managen an onberechenbar Verhalen ze moligéieren.

Benotzerdefinéiert Auer Management: Ëmsetze personaliséierten Uwendungsstrategien kënnen sécherstellen datt d'Donnéeën richteg an der richteger Zäiten hunn.

Benotzt vun Eda Tools: Modern elektronesch Design Automatesch (eda) Tools Offere fortgeschratt Anopperveraarbechtung.Dës Tools hëllefen an opzestellen a léisen a synchroniséieren Themen während der Kategorie Phase an der Leeschtung vun digitale Systemer mat digitale Systemer ze lancéieren.Si hëllefen Designer fir d'Identifikatiounsprobleemer fréi z'identifizéieren, garantéiert d'Finale Produkt ze fannen

Praktesch Uwendungen vun SR Latches

De SRC Latteniter, bekannt hunn fir hir Fäegkeet fir lues a verbreet ze gebrauchen, bleiwen dacks an ënnerschiddleche elektronesche System benotzt.Si exceléieren am Szenarie déi temporär Datenlagerung oder Staat Retentioun erfuerderen.

Temporär Datenlagerung

SR Laille ginn dacks an Cache Memory benotzt fir d'Donnéeën ze stockéieren.Dëst erlaabt de System bis siwel Daten, déi an esou dacks benotzte Daten aginn hutt destizontéieren d'Datebesdeeler an Efferstatiounen vu groussgeschriwwenen Prozess.

Späichere registréiert Dateien

An de Prozessoren, de SRSCHALLT GVCH BECALT Beim Aspektivitéite vun Donnéeën vun Daten a Reglementer am Registréieren, huet d'Veraarbechtungsprovitlung a gesamt d'Veraarbechtung a gudden System gemaach.

Kontrolléiere Kontroll Signaler

An der digitaler Kontrollsystemer, SR Latches sinn nëtzlech fir den Zoustand vun enger bestëmmter Kontrollsignaler ze halen, bis extern Bedéngungen oder System Logik diktéiert eng Ännerung.Och si hëllefen an de System ze behalen an de System, ganz konsequent Leeschtung an Operatiounen déi Präzisioun an Zouverlässegkeet brauchen.

Ausléiser a Konterkriibs

Sr latch-baséiert Flip-Flops ginn allgemeng benotzt a Circuiten déi synchroniséierter Operatioun erfuerdert, sou wéi digital Clocker an Timer.Si kontrolléieren zielen Puls, garantéiert eng korrekt Zäitpassung an zouverlässeg Leeschtung.Dës Zuelaufrend op SR Lawen ze beäntweren, korrekt zielen, déi sech op digante Systempierkungen näerten.

Mechanesch Interaktiounen

SR Latches si effektiv an eliminéiert mechanesch Boun an der Schalter.E mechanesche Bounce geschitt wann e Schalter-séier generéiert gëtt, repetitive Signal Ännerungen wéinst engem schlechten Kontakt.Sr Latches stabiliséieren den Ausgangssignal, verhënnert datt Feeler duerch noisy Signaler verursaacht.

Sr Flip-flop

En SR Flip-Flop, dacks genannt e Rand-ausgeléist Set-Reset Flip-Flop, besteet aus zwee interkonten SR Latches.Dës Dual-Latch Struktur erlaabt et op spezifesch Auer Signal Kanten ze äntweren (entweder erop oder falen) fir säi Staat ze änneren.Dëst gëtt duerch speziell Logikfroe tëscht de Latch erreecht.Den Outpropapp vum éischte Punktenn gëtt säin Inprip fir den Niveau vum Bilatt, an den Origin vun den zweete Latus, huet en Interchage vum ODCHOODINGT, erstallt.

Figur 7: SR Flip-Flop

De SR Flip-Flop ännert Staat präzis an der Auer Signal oder Falenrand.Den Interlocking Feedback tëscht den zwee SR Latches garantéiert datt de Flip-Flop nëmmen ännert sech als Äntwert op d'Auerrand, liwwert, stabil an zouverlässeg Ausgang.

Op Mikrofrozesser an digital Signal Prozessoren, SRP-Flops gi fir Datenclating a Lagerung benotzt.Si erfëllen an stabiliséieren Daten op spezifizéierter Auerkanten, garantéiert zouverlässeg spéider Datenveraarbechtung an Analyse.

Um Rand-Trigléiergank Mechismus hëlleft Rennen ze vermeiden, wou verschidde Deeler vum Kreesin oder Synchronisatioun ännert sech ouni Synchronisatioun, de Potentaliséiere sech an onbënschtvoll Ausgaben. Potenziell Outbuten.Sr Expla-Flops gi vertruedial an der Ëmsetzung diskutéiert fir spezifesch Kommunikatioun Logik, sou wéi Franchroniséierung a Feeler Opstellung.Hir Stabilitéit an FAST Äntwertzäit Hëllef Erhalen Daten Iwwerdroungquriktiounsqualitéit a System Zouverlässegkeet.

Verbueden Staaten am SR Latches an SR FLIPPS

Wann Dir SR Latches an SR Flip Flops benotzt an Nanz an nach GATES, mir hunn all néideg fir hemrendst Staaten ze vermeiden an ze vermeiden.E verbuedene Staat geschitt wann souwuel de Set (en) a reset (r) Inpute gläichzäiteg héich (fir Nand Gates) oder niddereg (fir nach eng Kéier.Dës Kombinatioun féiert zu engem onbestreiden Outputsstatus, wéi d'Ausput hänkt vum fréiere Staat vum fréiere Staat vun der Cirrika of.

Verbueden Staaten am Nan Gate SR Latches

Wéini béid s an r niddereg sinn, béid baussent héich ginn héich, wat verletzt d'Komplizit aus dem KuerzputstratDëst resultéiert an engem onbestänneg Staat.

Verbüdlech Staaten an der Nacher SR SR Latches

Wéini béid s an r héich sinn, souwuel Ausfäll ginn niddereg, en onbestänneg Staat ze kreéieren.Dëst kann zu onberechenbarem Behuelen ënnersträichen.

Praktesch Approche fir verbueden Staaten ze vermeiden

Füügt Kontroll Logik

Benotzt zousätzlech Logikpatten fir d'Staaten vum S an R. ze iwwerwaachen, wa béid Inputen Treff zu engem verbuedenen Zoustand anzepassen, automatesch en Input anzepassen fir den onbestriddene Staat ze vermeiden.Dëst garantéiert datt d'Ugräifer stabil bleift an prévisibel.Ëmsetzen eng logesch Paart déi intervenéiert wann s an r souwuel héich (oder niddereg) an upassen en Input fir e gültege Staat ze halen.

Software Simulatioun an Hardware Testen

Verhalen grëndlech Software Simulatioune fir potenziell verduebelt Staaten ënner verschiddene Bedreiwer Bedéngungen ze identifizéieren.Dëst erlaabt Designer ze gesinn an logesch Feeler Feeler virun der kierperlecher Ëmsetzung.Leeschtung extensiv Hardware Testen fir ze validéieren datt de Circuit mat all Inputkombinatiounen korrekt.Dëse Schrëtt hëlleft fir ze garantéieren datt d'Latch- oder Flip-Floper zouverlässeg an der realer Welt Szenarie.

Conclusioun

Wat d'Liewens- a Verbindheet vu SR deele kengem Bedeitung am Digital kreience d'Design.Wann den Ënnerbewäertung vum SOR iwwert hir Symol Representatioune gewénkt, a Saachen Dës Apparater, mir kréien op eng ëmfristeglech Verständnis a Gefor.Tr tr trotz de Pote fir eng vun hinnenutdriwwenen Staaten am Thyncchoneschen Designen, strategeren zesummen d'Kontroll vun Kontroll dës Refäriatioun kënnen dës vollwäert gin.Erhuele verstoppt elektronesch Design Automatifikatioun (Eda) Tools verbesseren d'Zouverlässegkeet an d'Leeschtung vun der Ernärung vun der Circuiten an d'Synchroniséierung.Ob a méigleche Konslerenzen (Fehlungsindeelung oder Feeler sinn, soll d'Fichieren an effizient digital Systemer agin ginn.Hir Roll an der héijer Geschwindegkeetsmëttelen an d'Synchronen Datenveraarbechtung a komplexer Uwendungen, déi hir endlech Relevanz befreit ginn.Watts - Uschlëss, d'Prinzipien SR d'SR d'Innovatiounen nëmmen Innovatiounen nëmmen Innovatiounen nëmmen Innovatiounen nëmmen Innovatiounen informéieren an eng zigell Elekskonten a inspiréierter Elementer, fir datt dës reproitäresch Aktivitéite vu sammelen, datt dës reproitesch Fonseien a sammelen Autorisal fir eng Entwécklung vu subbertalen

FROEN FROCESS [FAQ]

1. Wat ass en SR Latch?

En SRSCHA, oder Set-Reset Latch, ass e fundamental binäre Binärspäicherpersament an der digital Circuiten benotzt.Et ass en Thaynchronon Crécuit, dat seet Iech ouni Bocken Signal net refuséieren.

2. Wat ass d'Funktioun vum SR an der Logik?

Banneren, d'SR (Set-Reset) Inpute kontrolléieren den Zoustand vum Latch.

3. Wéi eng Zort Logik Gate mécht en SR Latch benotzt?

En SR Latch benotzt normalerweis entweder nach Gates oder Nandpatten.An engem Nour Gate-baséiert SRL Latch, den Ausgang vun all an den Zielen ass zréck an den Input vun deem aneren, e stabile Feedback-Loop.An engem Nand Gaart-baséiert SR Statch, e ähnleche Réckwardfroflaf dat benotzt gëtt, mee d'Iwwerliikodet komm, wat mat den Over Diage insgesäit geléierte sinn, och iwwer den Occascatch.Béid Konfiguratiounen erreechen déi selwecht Basisfunktionalitéit fir e binäre Zoustand op Basis vum Set an zréckzéien Input ze halen.

4. Wéi funktionéiert eng Latch?

E Latch schafft andeems Dir Feedback benotzt fir säin Ausgabstaat ze halen baséiert op den Inputen.An engem srlats, de Set (en) a reset (r) Inputen kontrolléieren den Zoustand vum Output (q).Wann de Set Input ageschalt ass (héich), den Ausgang ass op héich (1) gesat.Wann de Reset Input aktivéiert ass (héich), den Ausgang ass op niddereg (0).De Feideld bret am Etat vun dësem Film garantéiert datt eemol en Optrat gëtt, bleift et stabil bis en neien Input Signal ännert.

5. Wat ass den Nodeel mat engem SR Latch?

Déi primär Nodeeler vun engem SR-Shatch ass den ondefinéierte Staat deen geschitt wann béid (en) a reset (R) Inpute héich gläichzäiteg sinn.Dës Bedingung féiert zu engem onbestänneg Outputstate, wat d'Instabilitéit an onberechenbar Verhalen bei digitale Circuiten verursaache kann.Dëst "verbueden" Staat muss am Design vermeit ginn fir zouverlässeg Operatioun ze garantéieren.

SRPLAT, SIDS Signal, Direktkontrolle Curcuit, Binärspäicherpräis, ageriicht ass,error detection, aerospace applications, medical devices, circuit design, clocked SR latch, input signals, symbol and structure, high-speed memory, data buffers, timing control, precise control, state retention, microprocessors, digital signal processors, data sampling, dataVerspriechung, Delausmlaken, Gesetzpriechen, Srpla-Flop, Interbocken, Rue Deweidungsvisioun, Synchonung, Preisookroniséieren, obligatoresch Gleisungen, Spëtzen.Natierlech Beruffingen, kompenzubesch Lëtzebuergesch Konferenz-Systemer, mä net?