T ausgeléist Wëssen Guide - Virsiicht a Cons, wéi et funktionnéiert, Aarte

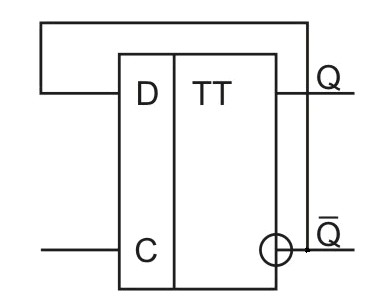

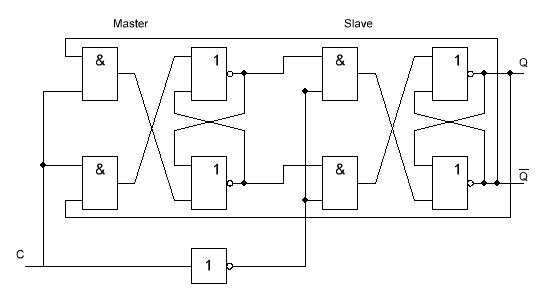

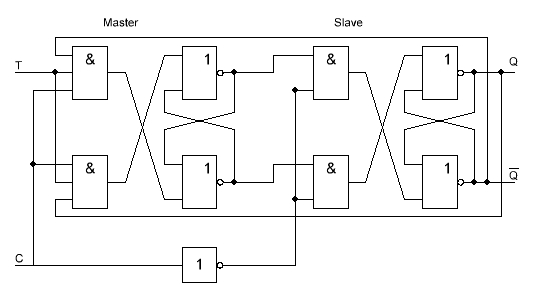

T-Flip-Flops sinn ähnlech wéi JK Flip-Flops.Andeems Dir de J an K Input verbënnt, kann een en T Flip-Flop ofgeleent ginn.Wéi en D Flip-Flop, et huet nëmmen een externen Input laanscht mat enger Auer.

Calalog

Wéi T-Flip-Flops Aarbecht

Flip-Flops sinn déi einfachst Geräter op digelat Automata, déi zwee stabile Staaten weisen.Ee Staat hält e Wäert vun "1" an deen aneren en "0." "Den Zoustand vum Apparat an déi binär Informatioun gespäichert ginn an et gëtt vun den Ausgangssignaler festgeluecht: direkten an inverse.Wann e Potenzial op den direkten Output plangt gëtt, entsprécht dem logeschen Output, den Apparat ass an engem eenzege-Ausléiserstaat (den inverse Outlist vum logesche Null).Wann et kee Potenzial um direkten Ausgang ass, ass den Apparat an den nullen Zoustand.

Aarte vun T-Flip-Flops

T-Flip-Flops kommen haaptsächlech an zwou Varietéiten:

Asynchronus T-Ausléiser

Synchronous t-Ausléiser

Béid Aarte vun T-Flip-Flops bedreiwen ähnlech.Deen eenzegen Ënnerscheed ass am Prozess vum Iwwergang vun engem Staat an dat anert.Den Asynchronous Typ mécht dës Iwwergank direkt aus, während de Synchrontypen op Basis vun dësem Signal.

Wann Dir zënter engem Szenario bewétiven wou d'Auer Input ëmmer héich (1) hutt, akzeptéieren, et ass no zwee pozyptesch Staatsstredes vun der Rullplack ze benotzen, entweder héich (1) oder 0).Loosst eis d'Resultater fir all Staat an der logescher Paart Interaktiounen involvéiert sinn.

Fall 1: t = 0

- Outputbestandung: Hei, souwuel Paart1 a Gate2 sinn a Gates verbonne mam T (op 0 gesat (op 0).

- Pate1 a Gate-opripséieren: zënter e puer Ablécksen 0 wéi vun hire Inspim; déi Rututs vum Paal1 a si stalte fir hir aner Inflëssegkeeten.

- Paart / Q (N + 1) Logik: Gate3 gëtt vun den Ausgang vum Gate beaflosst.Wann Gate1 Outputs 0, Gats3's logisesch Equatioun vereinfacht op net (0 oder net Q), déi zu Q.

- Gate4 / Q (n + 1) 'Logik: Gate4 follegt en ähnlecht Muster, deen net (0 oder Q), vereinfacht fir net Q oder q'.

Fall 1 Resumé:

- Ugeholl datt Gate1 = 0 an den Gate2 = 0 benotzt, an déi charakteristeschst vun a Gates benotzt (all Input vun 0 Resultater an engem Output vun 0),

- Gate3 / Q (n + 1) Computeren als Q, den aktuelle Staat z'erhalen.

- Paart4 / Q (n + 1) 'Resultater am Q', den Ergänzung vum aktuelle Staat.

Fall 2: t = 1

- Ausgangskonditioun: Wann t op 1 gesat ass, d'Input vum Gate1 an den Gate2 reflektéiert elo d'Ausgaben vun aneren Logik Operatiounen, déi hir Ausgaben beaflossen, beaflosst hir Ausgaben.

- Gate1 an Gate2 Output: Gate1 verbënnt direkt um aktuellen Zoustand Q, an ziel2 bis net Q oder q '.

- Gate4 / Q (N + 1) 'Logik: Hei, d'Equatioun vereinfacht, well d'Inputs vun der an der Torites sinn (q an net Q), deen an 0 ass)

- Gate3 / Q (n + 1) Logik: Op der anerer Säit, Gate3 Deals mat net Q oder Q ', Outputing net (q an 0), signifizéieren net q.

Fall 2 Resumé:

- De Logik Setup féiert zu interessanten Interaktiounen:

- PACK1 = Q, GATE2 = Q ', BEZUELT BEZUELT BENOTZT BENOTZT.

- Gate4 / Q (n + 1) 'frees direkt wéi 0, zënter der an Operatioun tëscht q an net ka net wouer sinn.

- Togin / Q (N + 1) dann ass Dir gär als ~, wat doméiss den ännert, wann ech 0 war.

T flip-flop Wourecht Dabo

|

Clk |

T |

Q (n + 1) |

Staatsministreg |

|

|

0 Boneier |

Q nous |

Keng Verännerung |

|

|

1 |

Q ' |

Talzkle |

Mir benotzen dëse Wourecht Dësch fir e charakteristesche Dësch ze kompenséieren fir den T Flip-Flop.An der Wourecht Dësch, kënnt Dir nëmmen een Input t an een Ausgangsk q (n + 1) gesinn.Wéi och ëmmer, am charakteristesche Dësch, gitt Dir zwee Inputen T an qn, an een output q (n + 1).

Aus der Logikdiagramm hei uewen, et ass kloer datt QN an QN 'sinn zwee Komplement Ënnerfälen, och als Inputs fir Gate3 and QN.n + 1) als Ausgang fir den nächste Staat.

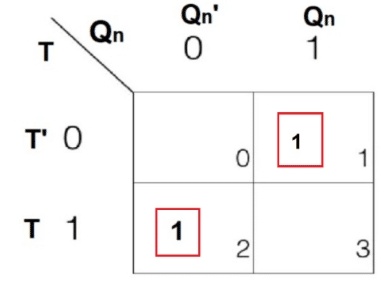

Nodeems Dir de charakteristesche Dësch ofgeschloss hutt, wäerte mir eng 2-Variable K-Kaart bauen fir déi charakteristesch Equatioun ofgeleet.

|

T |

Un |

Q (n + 1) |

|

0 Boneier |

0 Boneier |

0 Boneier |

|

0 Boneier |

1 |

1 |

|

1 |

0 Boneier |

1 |

|

1 |

1 |

0 Boneier

|

Vun der K-Kaart, kritt Dir zwee Pairen.Solving béid, mir kréien déi folgend charakteristesch Equatioun:

Q (n + 1) = tqn '+ t'qn = t xor qn

Virdeeler vun der T-Flip-Flops benotzen

Déi gréisste Criewercher ze fannene wéineg Quiums, T-Schippe kafen déi hir Funktioun an Integratioun vereinfachen:

- Eenzeg Input Simplicitéit: T-Flip-Flops hunn nëmmen een Input, hir Operatioun vereinfacht.Dësen eenzegen Input kann ignoréieren tëscht héijen an nigeléierte Staaten, et soll et intazulos integréieren integréieren an einfach mat aneren digitale Circuits verbannen.

- Keng ongëlteg Staaten: T-Flip-Flops feelt ongëlteg Staaten, hëlleft onberechenbar Verhalen an digitalen Systemer ze vermeiden.Dës Zouverlässegkeet ass entscheedend fir konsequent System Performance.

- Reduzéiert Kraaftverbrauch: Verglach mat anere Flip-Flops, T-Flip-Flops verbrauchen manner Kraaft.Dës Energieeffizienz ass profitabel fir d'Batterie Liewensland vum portabele Geräter ze verlängeren an d'Energiekäschte vu groussen digitale Systemer ze reduzéieren.

- Birkbar Operatioun: Wéi aner Flip-Flops, T-Flip-Flops Feature Bistable Operatioun, dat heescht datt se onendlech entweder state halen (0 oder 1) bis zu engem Inputel Signal.Dës Charakteristik ass wesentlech fir Applikatiounen déi stabil ze erfuerderen, laangfristeg Späichere vun allen-bit Daten.

- Einfach Implementéierung: T-Flip-Flops kënnen einfach mat Basislogikpatch ëmzesetzen.Dës Einfachmliusitéit mécht se e wirtschaftsstromydamëschent Paropsprogrammer fir vill digitalt Systems, hëllefen d'gesond ze reduzéieren.

Aschränkungen vun T-Flip-Flops

Och trainéieren dësen Virdeeler, T-Schipp fussen och e puer Aschränkungen déi hir Stellabilitéiten fir gewësse Uwendunge kann beaflossen:

- Invertéiert Ausgang: Den Output vu Flapell Flops ass de Géigendeel vun hirer Inpript, wat den Design vun der Timoricituren komplizéiert kënnt a mam Timoricitikreif komplizéiert kënnt an den Design méi komplex maachen.Designer mussen dëst bedenken fir e richtege Circuit Verhalen ze garantéieren.

- Limitéiert Funktionalitéit: T-Flip-Flops kënnen nëmmen e bëssen Informatioune späicheren an net fäeg sinn komplex Operatiounen wéi Zousatz oder Multiplikatioun ze maachen, limitéieren hir Notzung fir hir Benotzung an Basis Mémocken.

- Empfindlechkeet op Glitches: T-Flip-Flops kënne sensibel sinn fir Glitches a Geräischer op der Input Signal, potenziell onerwaart Staat Ännerungen ze verursaachen.Dës Empfindlechkeet kann zu onberechenbarem Verhalen an digitaler Systemer féieren, besonnesch an Ëmfeld mat héijer elektronesch Amëschung.

- Propagatioun Retard: Wéi all Flip-Flops, T-Flip-Flops Präsizéierung D'Präzatiounspiller, déi d'Timing Themen a Systemer mat strikte Timendrestungen an der strenger Timendranten sinn.Dës Zielunge mussen wärend dem System Design ugezeechent ginn fir Zäitfehler ze vermeiden an ze garantéieren

Uwendungen

T-Flip-Flops ginn a verschiddene real-Welt Uwendungen benotzt:

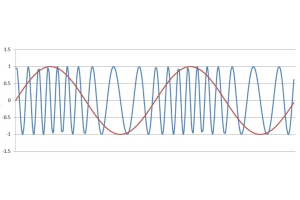

- Frequenz Divisioun: T-Flip-Flops ginn dacks benotzt fir d'Frequenz vun engem Auer Signal ze havelen.Andeems Dir den Zoustand vun der Flip-Flop mat all Clow Pulsiven, si beaflossen d'Frequenz vum Input Signal vun zwee, maachen se ideal fir präzis Timingen an Zoufälleg.

- Frequenz verduebelt: Conversey, T-Flip-Flops kënnen och benotzt gi fir d'Frequenz vun engem Auer Signal ze bekämpfen, bekannt als Frequenz ze verduebelen.Dëst gëtt erreecht andeems Dir d'Flip-Flops an engem Setup konfiguréiert, déi eng Ausgab Frequenz zweemol déi vum Input Signal generéiert gëtt.

- Daten Späichere: T-Flip-Flops kënnen als Basisbau Blocks benotzt gi fir eenzel Datenblécker ze späicheren, wou Daten temporär z temporär fir eng weider Veraarbechtung oder Iwwerdroung ze späicheren.Dëst mécht se ganz nëtzlech an der Uwendungen wéi Verréckelungsregisteren a Späicherapparater.

- Counters: Eng aner bedeitend Uwendung vun den T-Flip-Flops schafen Binary Counters.Si kënnen internesséiert mat aneren digiture Logikscates fir Counters ze konstruéieren oder ze klammen oder d'Netzwierker baséiert op der Design Ufuerderunge.

Iwwert ons

ALLELCO LIMITED

Liest méi

Séier Ufro

Schéckt eng Ufro w.e.g.

→ Virdrun

Är Batterie vun Ärem Auto vun Ärem Auto vun Ären Auto vun Ärem Auto ass fettele Bedierfnesser fir all Autosbesëtzer, besonnesch wa se extrem Wiederfuerderunge passen.DEN KALT CRANKING INPS (CCA) Bewäertung ass eng onverzichtbar Moossnam fir d'Schwammschutz ze gräifen fir en Iessomaren en Ist...

D'Dynamik vun 1,5V Batteries weist net nëmmen hir kritesch Roll fir eng verschidden Arrang vun Apparater ze maachen, awer och hire räicher historeschen historeschen historeschen an technologeschen Kontext.Dës Batterie, déi a verschiddene Forme kennt, a Aa, AAA, AA-ANS, an Dellen, déi an enger a...

→ Nächst

Wéi vill wësst Dir iwwer CCA?

op 2024/04/26

1.5V Batterie - Wéi vill wësst Dir?

op 2024/04/25

Populär Posts

-

Wat ass d'GND am Circuit?

op 1970/01/1 2940

-

RJ-45 Connector Guide: RJ-45 Connector Faarfcode, Wiress Schemaen, R-J45 Uwendungen, RJ

op 1970/01/1 2501

-

Faser Connectorypen: SC VS LC an LC VS MTP

op 1970/01/1 2089

-

Stroum Oplëschtung vun Vendagen vun Eliminronik VCC, VDD, VE, VSS, a GND

op 0400/11/9 1895

-

Verglach tëscht DB9 an Rs232

op 1970/01/1 1765

-

Wat ass eng lr44 Batterie?

Elektrocizizieller, dee bulquitesch Kraaft, roueg provozéiert all Asft vun eisem Alldag, vun trivial Gadgeten zu Liewensgeldmoossname medizinesch Ausrüstung, se spillt eng stänneg Ausrüstung.Profau schafft Dir awer dës Energie, besonnesch, besonnesch hätt an aussergewéinlech ob effektiv se ass, ass keng einfach Aufgab.Et kënnt un dësen Hannergrond deen den Artikel ëmmer nach konzentréie...op 1970/01/1 1714

-

D'Fundamenter ze verstoen: Induktiounsbetrag, ankapaktanz

An der strenger Danzerkranzer vun elektrende Dometatiounsrooss, a gouf schëlleg Elementer Macetalen Elementer Maset Carriage Masistenz: Apraktik.All Barten vun all eenzeg Ziktiounen déi den dynamesche Rhythmus vum dynamesche Circulas diktéieren kënnen.Hei, mir stoppen sech un fir d'Klammen vun dëse Komponitiv ze entdecken, fir seng deieraarteg Insele benotzt an dat hannen-elektresch Indeels z...op 1970/01/1 1655

-

CR2430 Batterie ëmfaassend Guide: Spezifikatioune, Uwendungen an Vergréisserung zu CR2032 Batterien

Wat ass cr2430 Batterie?Virdeeler vun cr2430 BatterienNormierCr2430 Batterie UwendungenCr2430 EquivalentCr2430 vs cr2032Batterie Cr2430 GréisstWat fir ze kucken wann Dir de CR2430 an Equivalenten kaaftDateblat pdfOft gestallten Froen Batterien sinn d'Häerz vu klenge elektronesche Geräter.Zu de villenen verfügbaren sinn d'Coa Zellen eng primmesch Roll ze spillen, a Reiser, Beräich ze stellen.T...op 1970/01/1 1555

-

Wat ass rf a firwat benotze mir et?

Radio Frequenz (RF) Technologie ass e Schlësseldeel vu moderner Worklos Kommunikatioun, konstalléiert Daten Iwwerdroung iwwer laang Distanzen ouni kierperlech Statiounen ouni kierperlech Statiounen.Dësen Artikel läscht an d'Grondlage vun der RF, Erkläert wéi elektromagnetesch Stralung (EMR) mécht RF Kommunikatioun méiglech.Mir wäerten d'Prinzipien vun EMR erliichteren, d'Kreatioun a Kontr...op 1970/01/1 1541

-

Cr2450 vs Cr2032: Kann d'Batterie amplaz benotzt ginn?

Lithium magane Batterien hunn e puer Ähnlechkeeten mat anere Lithium Batterien.Héich Energie Dicht a laange Service d'Liewen ass d'Charakteristiken déi se gemeinsam hunn.Dës Zort Batterie huet d'Vertrauen an e Gonschten vu ville Konsumenten gewonnen wéinst senger eenzegaarteger Sécherheet.Deier Tech Gadgeten?Kleng Apparater an eisen Haiser?Kuckt ronderëm an Dir wäert se iwwerall gesinn.Ën...op 1970/01/1 1512