Komplett Guide op den Aarm7-baséiert LPC2148 Microcontroller

Emabedded System Design erfuerdert déi richteg Mikroprozessor Kärelen an d'Entwécklunginstruktiounen zum spezifesche Projet Bedierfnesser ze wielen.Den Aarm Prozessor ass eng super Wiel an dësem Feld wéinst senger Villsäitegkeet iwwer verschidden Industrien, aus mobilen Technologie fir Automobilesch Systemer.Dësen Artikel konzentréiert sech um Abs77-baséiert LPC2144IC8 Micocolllroll, dat scho fir seng staark an Adaptabilitéit bekannt huet.Mir schéiwe sech op seng Architektur a Prapliber, Wann Dir Andurder an hir funktionnéieren a potenziell Uwendungen ubitt.Calalog

Wat ass den Aarm7-baséiert (LPC2148) Microcontroller?

Aarm representéiert eng prominent 32-Bit Riff-Architektur, déi duerch Aarm hält, trëppelen als Kärplattform am Mikroprocessor Design.Seng Effizienz an Adaptabilitéit hunn et iwwer eng breet Papital vun Uwendungen appelléiert.Déi verbreed Entlaonung vun dëser Architrebich vun dëser Architdere huet am onfabgurgabelen Aarmblummen dobäigesat wéi eng seele Mäert ze kreéieren.

Schlëssel Semikalonductorspiller wéi Samsung an Ti aktivéiert Systemer-on-Chips (Socips) déi d'Aarm Architekture benotzen, hir Engagement fir dëst Dech.Dësen Trend verännert Aarm hir Fäegkeet fir d'Entwécklung vun de raffinéierte Konsumentekonsubsatronik, industrialschénger Maschinn ze treffen, a méi.Observatiounen am Maart Dynamics weisen d'Aarbesexcestion eng grouss Afloss op seng Integratioun an déi lescht Tech Produkter.

Den Aarm7-baséiert LPC2148 Microcontroller gëtt fir seng Effizienz an niddreg Kraaftofdrock gefeiert.Et fënnt extensiv Notzung an alldeeglechen Uwendungen wéi Automobilystemer a portabel Elektronik.Aarm Architektur eenzegaarteg Saldo Einfachheet mat der berufflecher Kraaft.D'Instruktiounsset gëtt verkafteg fir intuitiv ze sinn, erlaabt eng effizient Ausféierung an reduzéiert Entwécklung Zäit.Dës Ideologie proposéiert datt d'Einsamkeet verbessert anstatt auszeschléissen vun der Fäegkeet, gestrësst Produktentwécklung andeems se debugging an Ënnerhalt méi einfach maachen.

Den Aarm7 Prozessor

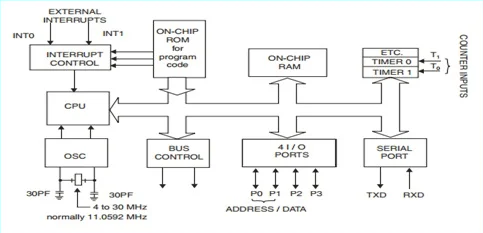

EMBEDDED Systemer fannen den Arm7 Prozessor eng Appeling Wiel wéinst wéi et klassesch Veraarbechtungsmethoden mat der evoluellen Cortex Architekturen.Seng Appel Stiele vu senger Affenheet beim Ëmgang vun der Ëmgangs Aufgaben, zerwéieren béid méi alen Technologien a pionéiert Fortschrëtter mat gläiche Finess.Den Arm7 Prozessor gëtt kompletéiert duerch eng extensiv Dokumentéierung vun Entreprisen, wéi nXP Hallefkanner.Dës Plethora vu Ressourcen AIDS NEWSLERS wéi se hir Fäegkeeten an Hardware a Software Design ernären.De lucide Guidance erliichtert eng méi einfach Léierkurve.

AMSRA7 Verschmitoren ginn am Consouper elektrive Kontrollen ugemeien, an och exotiv Kontrolls Kontrollen, an eng Industriente-Systemer.Hir Kapazitéit fir eng Rei vun Aufgaben vun enger richtende Grenzbänner ze managen, verlangt se Valitisatioun an der Ofsécherung vun der wirtschaftlecher Effizienz.Interaktéieren mat Air7 Mikriccontroller erlaabt d'Individuen souwuel thoretesch Wëssen an Handfäegkeeten ze verbesseren.Handelssystemer mat dëse Prozessoren kultivéiert eng Valorisatioun fir kréint Coding an Adept Ressource Courcet-Management, dacks kreativ Approche fir Problemer ze probéieren.D'Arrivum Archituratioun bitt eng d'Verbindung tëscht Konventioun fir d'Verkässer an modern Dechniken, behandelt seng Wichtegkeet an enger aktueller Féierung vum Stroumstechnologie.

De LPC2148 Microcontroller

D'LPC21448 Microcontroller, insafelitt vun NXP, déi eng Suite vu Funktiounen am Laf vun der Funktiounsfolater a fonnelile Reiecher an Ofleeele mussen.Operéiere vun engem 16-Bit oder 32-Bit Asb7. Prozessor Kéner, setzt se sech op e Spektrum vun der Demandeungen, béid Adaptabilitéit a Bewosstsinn ze weisen.

Verpackung a Programméierung

Ersetzen an enger Schleek LQFP64 Package, d'LPC248 Integréiert woufälleg Motivatiounen.Et ënnerstëtzt souwuel In-System an un--u-Plaquungsbegreifelen ze liwweren, sinn d'Sufgaben awork ze Upassung vun engem Exrocknement.Dëst erliichtert d'Belaaschtung fir Remote Apparater brauche dacks Updates fir Peak Performance an der Safguard Sécherheet ze halen.

Erënnerung a Geschwindegkeet

Bitt bis zu 40kb vun SRAM an 512kb vu Flash Memory, d'LPC248 Ops mécht Méiglechkeeten fir irrikant Programmer an Daten.Op d'Spits vu 62 mhz beréit, da kennt d'Demande vun der Uwendungen, déi op sappidéieren Datebankaarbecht an Ech representéieren an Ech representéieren.

Konnektivitéit an Interfaces

Si iwwer eng voll schnitesch Kontributme, séieren den LPC2438 garantéiert sécher den Digiddesträr a Säisslos Curatesch mat aneren digitativ Konsultativ Personal mat aneren Digelméissegkeetsspéineg.Dës Feature kënnt als Linchpin fir Kommunikatioun aus.

Analog an digital Konversiounen

Befestegt d'Annonce integréieren, dac, a multiple Timer, et exclizéiert an der präziser Analog an digital Signalveraarbechtung, rended Sense fir e korrigéiert Sensorzéngungen a Kontrollen ze kontrolléierenDéi niddereg-Kraaft RTC a verschidde Serien Interfaces Garantéiert konsequent Timeping an adaptable Kommunikatiounspunktioun.

Kraaftmanagement an Effizienz

Occaséiert fir eng zoutrilend Uwendungen, d'LPC218-28 Championsmuechtsmuechtsmoderen, Featuren, Feel-tolerant I / O, a bitt multipruptiounen.Seng Phas gespaarten Loop fir Auer Kontroll Harmoniséiert Kraaft Effizienz beim Curbing System Kaméidi fir Geräter déi op Batterien vertrauen.

LPC2148 Microcontroller Memory Architektur

De LPC2148 Microcontroller presentéiert en diverse Memory Setup mat 512kb vu Flash Memory an 32kb.Ideal fir verschidde embedded Applikatiounen, déi e multiple Controduktungsorache ënnerstëtzen, fellend stabil Datenenthalung iwwer Zäit.

On-Chip Flash Memory

Op-Chip Flash Memory Teignrifs mam JTAG an der Uart, ënner anerer, adaptabilitéit an der Propruging.Déi robust Ausdauer vun dëser Erënnerung ënnerstëtzt heefeg Schreift-läscht Zyklen, déi wäertvoll fir Szenarie verlaangen déi reegelméisseg Firmware Updates oder Daten Login.Seng konsequent Leeschtung Nidderen Zouverlässegkeet iwwer dës Aufgaben.

On-Chip SRAM

Mat 32kb vun der SRAM, dës Komponent verwandt.Temporär Daten Späicher wärend Héich-Geschwindegkeetsveraarbechtung ass glatten vun der SRAM, verhandelt Systemeffizienz an d'Reaktiounsfäegkeet.

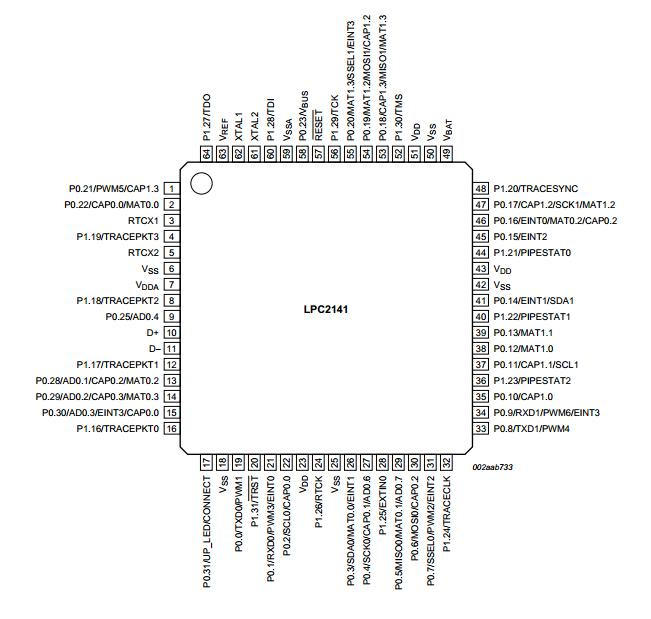

Input / Output Ports

Den LPC21448 huet zwee upaptéiert i / o port a pabelen, konfigéierte fir Funktiounen wéi GPIo an Uart applino.Dës Flexibilitéitsadresse verréckelte Applikatioun Ufuerderunge, déi Nahtless Projektrecht ausdrécken wéi Bedruch.Dës Feature optimiséieren Kommunikatiouns Protokolls a Boost System Adaptabilitéit.

Initiéiert effektiv Programméierungsstrategien

GPio Pins erfëllen Multiple Rollen a verschiddenen Uwendungen.Paken ptre a Ph1, bekannt fir hir Adaptabilung, enthalen PENS un hir Game net opgatoen hir Management ze bidden.Pakt P0 a P1 éierlech eng weiderfuerend Funktionalitéit, Caterial zu Daucherer Elektronik a Beruffsprojeten.Hir Adaptabilitéit invitéiert d'Benotzer fir d'Potenzen an d'Sotumware ze verdéngen, verlaangt eng Valorisatioun vu senger ustrengender Aarbechtsplazen.Engagéiert Handy mat dësen Konfiguratiounen déi seng Fäegkeet verflicht fir kompüngend Komplex Szenarie ze navigéieren.Register Registriär ze managen d'Personnalisatioun vun soss net erreechbar Pins, an eenzegen Uwendungsofhängeger.Si erlaben fir dynamesch Ännerungen, eng Notioun fir Leeschtungverweisung.Fäegkeet vun dësen Ëmgank vun dësen Konfiguratiounen erreecht eng harmonesch Gläichgewiicht tëscht operationeller Bedierfnesser an Ressource.

Aarm7-baséiert (LPC2148) Pin Konfiguratioun

|

Petzlech Zuel |

PIN Numm / Funktioun |

Broessdatsch |

|

1 |

P0..21 / pwm5 / Cap1.3 / ad1.6 |

GPio, PWM Output 5, Timer 1 Capture 3, Adc Input 6

(LPC2144 / 46/48) |

|

2 |

P0..22 / Cut0.0 / ad1.7 / Mat0.0 |

GPio, Timer 0 Capture 0, adc Input 7 (LPC2144 / 46/48),

Timer 0 Match 0 |

|

3. |

RTXC1 |

Input zu RTC Oscillator Circuit |

|

4

|

Tracepkt3 / P1.19 |

Spure Packet 3, GPio |

|

5- |

RTXC2 |

Ausgang vum RTC Oscillator Circuit |

|

6, 18, 25, 42 Joer 50 |

Terrain (GND) |

Ground Referenz Pins |

|

7 |

Vdda |

Analog Volet Power Supply (3.3V) |

|

8 |

P1.18 / Tracepkt2 |

GPio, Spuer Packet 2 |

|

9 |

P0..25 / Aoutout / Ad0.4 |

GPio, Dac Output (LPC2142, 2144, 2146, 2148), AC Input 4 |

|

10 |

D + |

USB D + Linn |

|

11 Mee |

Drei |

USB D- Linn |

|

12 |

P1.17 / Tracepkt1 |

GPio, Spuer Packet 1 |

|

13 |

P0.28 / Cap0,2 / ad0.1 / Mat0.2 |

GPio, Timer 0 Capture 2, ADC Input 1, Timer 0 Match 2 |

|

14 |

P0..29 / Cap0.3 / Ad0.2 / Mat0.3 |

GPio, Timer 0 Capture 3, ADC Input 2, Timer 0 Match 3 |

|

15 |

P0.30 / eint3 / ad0.3 / Cap0.0 |

GPio, extern Ënnerbriechung 3, adc Input 3, Timer 0 Capture

0 Boneier |

|

16 |

P1,16 / Tracepkt0 |

GPio, Spuer Packet 0 |

|

17 |

P0.31 / Up_led / Connect |

GPio, USB Upnlink Status huet gefouert, mëll Connect Feature Kontroll |

|

19 |

P0.0 / pwm1 / txd0 |

GPio, PWM Output 1, UART0 TX |

|

20 |

P13.1 / BENG |

GPio, JTAG Test Reset |

|

21 WEISEN |

P0.1 / pwm3 / rxd0 / eint0 |

GPio, PWM Output 3, UART0 RX, extern Ënnerbriechung 0 |

|

22 sinn |

P0..2 / Cap0.0 / Scl0 |

GPio, Timer 0 Capture 0, I2C0 Auer |

|

23, 43, 51 Joer |

Vdd |

Power Versuergungspannung fir i / O Ports an de Kär |

|

24 |

P1,26 / RTCK |

GPio, zréckginn Test Auer fir JTAG |

|

26 26 |

P0,3 / SDA0 / Mat 7,0 / Eint1 |

GPio, I2C0 Daten, Timer 0 Match 0, extern Ënnerbriechung 1 |

|

27 Been |

P0.4 / Cap0.1 / Sck0 / ad0.6 |

GPio, Timer 0 Capture 1, Spi Clock, Adc Input 6 |

|

28 Traitegkeet |

P1.25 / Ausstierm |

GPio, externen Ausléiser Input |

|

29 Iwwer déi 29 |

P0.5 / Mat0.1 / Miso0 / ad0.7 |

GPio, Timer 0 Match 1, Spi Miso, adc Input 7 |

|

30 |

P0.6 / Mosi0 / Cap0.2 / AD1.0 |

GPio, SPI Mosi, Timer 0 Capture 2, ACC Input 0

(LPC2144 / 46/48) |

|

31 |

P0.7 / PWM2 / SLS0 / Eint2 |

GPio, PWM Output 2, Spi Sklave wielt, extern Ënnerbriechung

2 |

|

32 |

P1..24 / Traceclk |

GPio, Spurkock |

|

33 Aarbecht |

P0.8 / txd1 / pwm4 / ad1.1 |

GPio, UART1 TX, PWM OUTPUT 4, ACP Input 1 (LPC2144 / 46/48) |

|

34 Ëmpf no 34 |

P0.9 / pwm6 / rxd1 / eint3 |

GPio, PWM Output 6, UART1 RX, extern Ënnerbriechung 3 |

|

35 |

P0.10 / RTS1 / Cap1.0 / AD1.2 |

GPio, UART1 RTS, Timer 1 Capture 0, Adc Input 2

(LPC2144 / 46/48) |

|

36 |

P1.23 / Pipestat2 |

GPio, Pipeline Status Bit 2 |

|

37 |

P0.11 / Capp1.1 / CTS1 / SCL1 |

GPio, Timer 1 Capture 1, UART1 CTS, I2C1 Auer |

|

38 i |

P0.12 / Mat1.0 / AD1.3 / DSR1 |

GPio, Timer 1 Match 0, adc Input 3 (LPC2144 / 46/48), UART1

DSR |

|

39 Ëmen |

P0.13 / Dtr1 / Mat1.1 / AD1.4 |

GPio, UART1 DTR, Timer 1 Match 1, adc Input 4

(LPC2144 / 46/48) |

|

40 Veräin |

P1.22 / PipeStat1 |

GPio, Pipeline Status Bit 1 |

|

41 HUNN !!! |

P0.14 / DCD1 / Eint1 / SDA1 |

GPio, UART1 DCD, extern Ënnerbriechung 1, I2C1 Daten |

|

44 |

P1.21 / Pipestat0 |

GPio, Pipeline Status Bit 0 |

|

45 Ë5 |

P0.15 / Eint2 / Ri1 / ad1.5 |

GPio, extern Ënnerbrieche 2, UART1 RI, ADC Input 5

(LPC2144 / 46/48) |

|

466 |

P0.16 / Mat0.2 / eint0 / Cap0.2 |

GPio, Timer 0 Match 2, extern Ënnerbriechung 0, Timer 0

CAPTURE 2 |

|

47 Méibëlleg |

P0.17 / SCK1 / CAP1.2 / Mat1.2 |

GPio, SSP SCK, Timer 1 Capture 2, Timer 1 Match 2 |

|

48 |

P1.20 / Tracesync |

GPio, Trace Synchroniséierungssignal |

|

49 Bei 49 B. |

Vbat |

Stroumversuergung fir den RTC |

|

52 Ënnert mechsten |

P1.30 / TMS |

GPio, Testmodus wielt fir JTAG |

|

58 Ëkf-53 |

P0.18 / Cap1.3 / Miso1 / Mat1.3 |

GPio, Timer 1 Capture 3, SSP Miso, Timer 1 Match 3 |

|

54 54 |

P0.19 / Mosi1 / Mat1.2 / Cap1.2 |

GPio, SSP Mosi, Timer 1 Match 2, Timer 1 Capture 2 |

|

555 |

P0..20 / sels1 / Mat1,3 / eint3 |

GPio, Ssplave Wielt, Timer 1 Match 3, extern

Interberéiert 3 |

|

5,6 |

P1,29 / Tck |

GPio, Test Auer fir JTAG |

|

57 Ëmeier |

Extern Reset Input |

Reset den Apparat op Standardbedingunge |

|

58 |

P0..23 / vbus |

Beweist d'Präsenz vun der USB Busmuecht |

|

59 |

Vssa |

Analog Terrain, getrennt fir Geräischer a Feeler ze reduzéieren |

|

60 |

P1.28 / TDI |

GPio, Testdaten Input fir JTAG |

|

61 Gutt |

XTAL2 |

Ausgang vum Oscillator Verpflichtung |

|

Nee 62 |

Xext1 |

Input an den internen Auer Generator an OSCillator

Circënts |

|

63. |

Vref-adc Referenz |

Nominal Spannung fir adc Referenz, getrennt ze reduzéieren

Feeler a Geräisch |

|

64 Oawom |

P1,27 / TDO |

GPio, Testdaten Ausgang fir JTAG |

Conclusioun

Den Aarm7-baséiert LPC2148 Microcontroller déngt als dynamesch an adaptable Plattform fir embedded Systemer.D'LPC21148 gëtt fir d'viverte Felder als Konsumentepronikoti virgefouert an industriellunioun wéinst senger flexibelléiert Architektur.Dëst Flexibilitéit Investitions an Innovatioun.Seng Fäegkeeten verlängeren sech einfach Aufgaben ze handelen fir komplex Operatiounen ze ausféieren, sengsäite sengsäitlech Natur ze weisen.De LPC2148 bleift e gewënschte Tool fir säin dauerhaften Impakt an engem jee-ännert Tech Secteur.

Iwwert ons

ALLELCO LIMITED

Liest méi

Séier Ufro

Schéckt eng Ufro w.e.g.

Stm32l vs stm32f: e ëmfraenesche Guide fir hir Differenzen an Uwendungen

op 2024/10/2

13009d Transistor erkläert: Spezifikatioune, Uwendungen, a gläichwäerteg Modeller

op 2024/10/1

Populär Posts

-

Komplex Instruktiouns Set Computeren: Wéi hunn se Computeren geännert?

op 8000/04/18 147768

-

USB-C Pinout a Features

op 2000/04/18 111996

-

Mat XILINX vereenegt Simulatiounspriminits: e verständleche Guide op FPGA Design an Simulatioun

op 1600/04/18 111351

-

Energieversuergungsspannungen an der Elektronik: Bedeitung vu VCC, VDD, VEE, VSS a GND

op 0400/04/18 83764

-

RJ45 Connector Guide: Pinout, Wirbelen, Kabelaarten, a benotzt

op 1970/01/1 79555

-

Den ultimativen Guide fir e Faarfcode a modernen elektresche Systemer

De Wee wéi eis elektresch Systemer benotze Faarwen net just fir ze kucken.All Drot Faarf elo eng spezifesch Funktioun ze weisen, mécht et méi einfach ze identifizéieren an elektresch Komponenten ko...op 1970/01/1 66956

-

Purge Valve Guide: Funktioun, Symptomer, Testen, an Ersatz fir optimal Motor Leeschtung

De Purge Ventil ass e Schlësseldeel vun engem Autosystem dat hëlleft der Loft ze halen andeems Dir Brennwampfabuer behalen ier se an d'Atmosphär flucht.Dëst ass net nëmmen der Ëmwelt andeems Dir d'...op 1970/01/1 63098

-

Qualitéit (q) Faktor: Equatiounen an Uwendungen

De Qualitéitsfaktor, oder 'Q', ass wichteg wann se ze kontrolléieren wéi gutt Induktoren an Elektoren an elektronesch Systemer déi Radiquenzen benotzen (RF).'Mitymëll wéi och ëmmer Quellen mimitt a...op 1970/01/1 63029

-

Erreechen Peak Leeschtung mat der maximaler Kraaftdransporter vum

De Maximum Power Transfert Den Transfer erkläert wéi Energie vun enger Quell, sou eng Batterie oder Generator, fléisst op eng verbonne Last.Et weist de genaue Konditioun wou d'Belaaschtung déi mees...op 1970/01/1 54095

-

A23 Batterie Spezifikatioune an Onméiglechkeet

D'A23 Batterie ass eng kleng, Zylinder-förmlech Batterie mat Héichspannung.Och genannt 23a, 23aascht oder Mn21, leeft et um 12 Volets a vill méi héich wéi AA oder AAA Batterien.Säin spezié...op 1970/01/1 52176