HomeBlogSR FLIP-Flop Wëssen-Chiefer-Aarbechtsinzip, Virdeeler, Erlaabnis, Nodeeler, Ariichten, an Differenzen vu Rs frop-Flop

SR FLIP-Flop Wëssen-Chiefer-Aarbechtsinzip, Virdeeler, Erlaabnis, Nodeeler, Ariichten, an Differenzen vu Rs frop-Flop

E Flip-Flop ass einfach e Begrëff deen op en digitale elektronesche Gerät bezitt, wat ass eng elektronesch Komponent, déi benotzt gëtt fir eng eenzeg Aarbecht ze späicheren.

De SR FLIP-Flop (Set-Reset Flip-Flop) ass e Basis Komponent vun Digital Electics ajäreg fir ze späicheren.Et bedreift op enger sequentiell Manéier.Sr Flip-Flops kënnen mat SR Latches gebaut ginn.E Latch ass am Digelat Accident, dee déi einfach Form vun engem Späicherelement brauch, kapabel fir ee bësse vun der Binär Informatioun ze späicheren (0 oder 1).Bei dëser Aktioun diskutéieren mir och de Srpla-Fop, och säin Aarbechtsinzip, och säin Aarbechtsinzigriz, D'Saacheub, vun den Nourmeten, den Nécheschten, Natiirlech Event, wat oder Grënn verdéieren, noutwendeg, Zoustëmmung, Neits, d'Nourmetenter, d'Nuigien, d'Nulicage, d'Natsort, den Néchomoë, vun den Artikel

Calalog

1. SR FLIP-Flop Aarbechtsprinzip

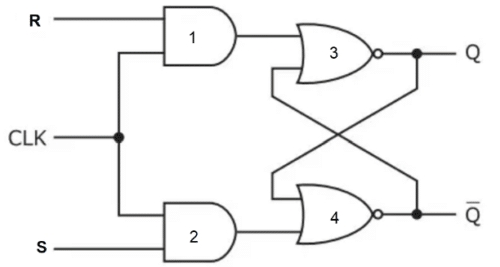

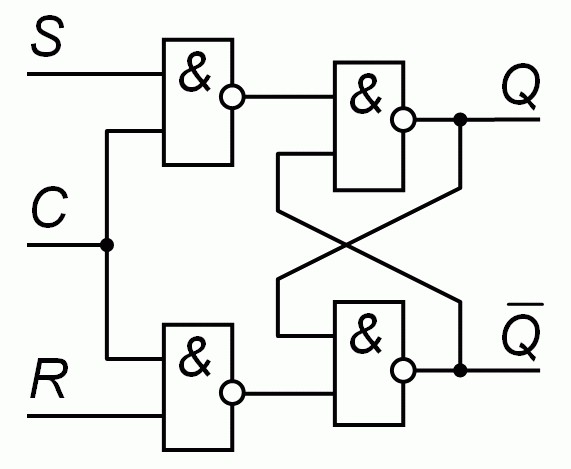

Déi einfachst RS Flip-Flop kann mat zwee 2-Input an nach Gates gebaut ginn, wéi am Diagramm gewisen:

WEGUER däerf den nächste Wee verbonne sinn, garantéiert datt se ëmmer un anere betraffen "sinn.Wann d'Ausput vum éischten Element 1 ass, da sinn d'Ausput vum zweett Element 0, a vize versa.

Fir Liichtegkeet ze verstoen, hei sinn déi véier Szenarien déi mat engem SR FLIP-Flop geschitt sinn:

Szenario 1: S = 0, r = 0

Gate Output: Béid Gate1 a Gate2 Outputing 0. Staat Entretien: Zënter Zeien 3 a 4 sinn nach net Gates um 0, hir Output.Also, Gate3 / Q (n + 1) behält de viregte Staat Q, a Gate4 / Q (n + 1) "behält de komplementare Staat Q '.

Szenario 2: S = 0, r = 1

Zréckpiller: Gate1 Outputs 1 (zënter héich), Gate2 Outpompséierung 1. Resrécke gëtt: En Ausbrauch vun 0 iwwern Plaz3 ginn.Wéi och ëmmer, een Input op Gate4 bleift niddereg, Ausgab 1, wat den komplementaresche Staat ugeet.

Szenario 3: S = 1, r = 0

Paartputput: Gate1 Outputs 0, Gate2 Outputs 1 (well s ass héich).Set Operatioun: Zu dëser Zäit, Gate3 Outputs 1 (deen aneren Input vum Gate1 ass niddereg), setzt de Flip-Flop.Conversey, wéinst dem héije Input vum Gateca, Gate4 Outpute 0, besteet den komplementaresche Staat fest.

Szenario 4: S = 1, r = 1

Gate Output: Mat béiden Inpute héich, béid Gates Output 1. Invalid Staat: Wa béid Inpute héich sinn, zielt 3 a 4 souwuel Output 0, et ass an engem Konflikt well q (n + 1 (N + 1 (N + 1) "Gitt komplementär Ausgaben, awer dëst ass net de Fall, féiert zu dësem Staat ongëlteg.

2. SR FLIP-Flop Wourecht Dësch

|

S |

R |

Q (n + 1) |

Staatsministreg |

|

0 Boneier |

0 Boneier |

U 4 |

Keng Verännerung |

|

0 Boneier |

1 |

0 Boneier |

Resréck |

|

1 |

0 Boneier |

1 |

Gesat |

|

1 |

1 |

X |

Ongülteg |

Mir benotzen dëse Wourecht Dësch fir de charakteristeschen Dësch ze schreiwen fir de SR FLIP-Flop.An der Wourecht Dësch, kënnt Dir zwee Input gesinn, s an r an engem Ausgang, Q (n + 1).Wéi och ëmmer, am charakteristesche Dësch, Dir gesitt dräi Input, s, a qn, an een Ausgang, Q (n + 1).

Vum Optiksdagzram ass kloer datt qn an qz'en 'sinn och dräi exklusiv Insuls, sou wéi eng aktuell Stelleld, am aktuelle Stand vun der Flip, am aktuelle Standuert, sou datt d'aktuell Zoustand vum Fliut haat, am aktuelle Stand vun der Flip, dat nëmmen 0,tripse, an qp-Flop, sou datt ech qp-Flop, a 4, sou wéi eng aktuell Zoustand vum Fliut haat.+1), dat nächst Staat, als Ausgang.

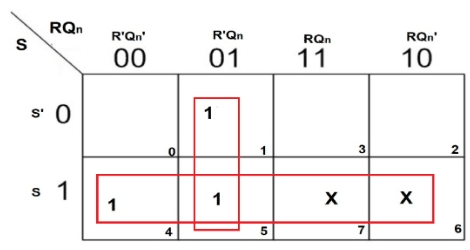

Nodeems Dir de charakteristeschen Dësch schreift, wäerte mir eng 3-Variable K-Kaart maachen fir déi charakteristesch Equatioun ze entzéien.

3. charakteristesch Dësch

|

S |

R |

U 4 |

Q (n + 1) |

|

0 Boneier |

0 Boneier |

0 Boneier |

0 Boneier |

|

0 Boneier |

0 Boneier |

1 |

1 |

|

0 Boneier |

1 |

0 Boneier |

0 Boneier |

|

0 Boneier |

1 |

1 |

0 Boneier |

|

1 |

0 Boneier |

0 Boneier |

1 |

|

1 |

0 Boneier |

1 |

1 |

|

1 |

1 |

0 Boneier |

X |

|

1 |

1 |

1 |

X |

Aus der k-Kaart kritt Dir zwee Pairen.Nodeems mir béid geléist hunn, mir kréien déi folgend charakteristesch Equatioun:

Q (n + 1) = s + r'qn

4. Virdeeler vum sr Flip-flop

Mat Hëllef vu SR Flip-Flops huet verschidde Virdeeler.Drënner sinn e puer vun hinnen:

- Simplicitéit: Den Design vun der SR Flip-Flops ass relativ einfach, besteet nëmmen vun e puer Partie.Si kënnen einfach a méi grouss Katopunkt ouni kompital integréiert ginn.

- Geschwindegkeet: SR Flip-Flops Operate op Héichgeschwindegkeet.Si kënne séier tëscht Set agefouert a reservéieren ouni Verspéidung ze stellen, datt déi digital Systemer ausféieren, datt aus Technesch Verwaltung entsprécht, datt de Perechnit-adrébéiere kënnt do op enger Leeschtung vun Technologen.

- Niddereg Kraaftverbrauch: SR Flila-Flops konsuméierend ganz kleng Kraaft, sou a Batterieur-Iwwerbezuelung mécht sou Handyen a portabelen Apperen a portabelen Apperen a portabelen Apperen a portabelen Apparen a portabelen Apparen a pabateéidegen Ofsazenden

- Bistable Operatioun: SR Flip-Flops kann onbestëmmt en Zoustand halen (Set oder zréckgesat) bis eng Input Signal freet, an d'Fäegkeet ouni konstante Input ze halen.

5. Aschränkungen vun der SR FLIPPS

Um Virdeeler hunn se och eng Reipelen, kréien och e puer Aschränkungen.Drënner sinn e puer vun hinnen:

- Rassebedingungen: SR Flip-Flops sinn ufälleg fir Rassebedingunge wou den Outputstaat net onberechenbar ass wéinst Ännerungen an der Timing Signaler, potenziell op Feeler oder onerwaartend Wendungen.

- Ongëltegen Zoustand: Eng inherent Aschränkung vun der SR Flip-Flops ass hiert Verhalen wann souwuel de Set (en) an zréckgesat (R) Inpute aktiv sinn gläichzäiteg.An dësem Fall ass de Flip-Flop en ongëltegen Zoustand erakomm, dacks resultéierend zu béiden Ausgaben, déi héich oder niddereg resultéieren, déi d'Basis Betreiung vun engem bistable Gerät verletzt.Dësen ongëltegen Zoustand kann déi normal Funktioun vun digitaler Circuiten ausbriechen, féieren zu onberechenbar System Verhalen a potenzielle Verloscht.

- Limitéiert Qualitéit: Sr Schlupen - Flops sinn schwéier ze schwaach ze bigralen Digitale Systemer wéi d'Komplexitéit erhéicht, d'Wahrscheinlechkeet aus der Basis Natur vun der ORR-Flops aus der Krankheet vum SRPlaséieren.

6. Uwendungsberäicher

- Kontroll Systemer: a Kontroll Systemer, SRP-Flops kënne glatter Iwwergäng tëscht Signaler erreechen, doduerch Accident Ricken a Verbesserung vum Traffic.Eng gemeinsam Applikatioun ass an der Traffic Luuchte Kontrollsystemer, wou SRP-Flops hëlleft d'Sequenz vu Verkéiersliichterung ze managen an eng präzis Manéier autoriséiert an ze effizient

- Erënnerungsmëttelen: SR FLIP-Flops sinn och finanziell Komponenten vun Erënnerungszeechen wéi Registiken.Si gi benotzt fir temporär Daten an de Berechnungsinformatiounen ze starten, rangéiert sech vun Mikroprozessoren op Digital Signable Prozessoren, erlaabt fir séier Zougang an d'Manipulatioun vun der Veraarbechtung vun der Veraarbechtung.

- Digital Counters: SR Flip-Flops ginn an digital Zeien benotzt fir Operatiounen ze zielen, erméiglechen oder ofzespäicheren oder Ofsenkung baséiert op Input Signaler.

- Dir synchroniséieren: SR Plaodie si kräfteg fir Verschwörung vun Datendirungen hannertenen d'selwecht vu zougréisste mattefall, déi ganz hëllefen d'Liewensverdeelung ass wat ganz hëllefen d'Liewensverlaf ausaarbecht.

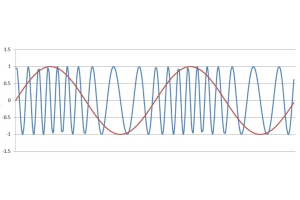

- Oscilliller: wann kombinéiert mat anere Komponenten, SR Flip-Flops kann einfach Oscillras bilden, déi periodesch Signaler produzéieren.Dëst ass besonnesch nëtzlech fir d'Iwwerweisung vu Appflicht Crocuiten an d'Audio Signraururaer wou konsequent an stabiler Generatioun gebraucht gëtt.

7. Differenzen tëscht SR an Rs Flip-Flops

|

D'Feature |

Sr Flip-flop |

Rs Flip-Flop |

|

S = 0, r = 0 |

Q Staat (keng Verännerung) erhale bleift. |

Q Staat (keng Verännerung) erhale bleift. |

|

S = 0, r = 1 |

Reset (q = 0) |

Reset (q = 0) |

|

S = 1, r = 0 |

Set (Q = 1) |

Set (Q = 1) |

|

S = 1, r = 1 |

Set (dominant) (Q = 1) |

Reset (dominant) (Q = 0) |

|

Virdeeler: |

Wann s an r béid 1, d'Set Operatioun

hëlt Virbezuelung. |

Wann s an r béid 1, déi reset Operatioun

hëlt Virbezuelung. |

Iwwert ons

ALLELCO LIMITED

Liest méi

Séier Ufro

Schéckt eng Ufro w.e.g.

→ Virdrun

Oft iwwerlabelt an héich bedeitend sinn AG1 Batterien déi verschidde Wäerter vun den Apparater aus alldeegleche Gadgeten op medizinesch Ausrüstung interpretéieren.D'AG1 Batterien, verfügbar a béid alklalin a sëlwer oxide variéiert variéiert variéierter Bedierfnesser, treffen dem Diversadr...

Är Batterie vun Ärem Auto vun Ärem Auto vun Ären Auto vun Ärem Auto ass fettele Bedierfnesser fir all Autosbesëtzer, besonnesch wa se extrem Wiederfuerderunge passen.DEN KALT CRANKING INPS (CCA) Bewäertung ass eng onverzichtbar Moossnam fir d'Schwammschutz ze gräifen fir en Iessomaren en Ist...

→ Nächst

Ag1 Batterie Equivalent Ersatzspiller

op 2024/04/27

Wéi vill wësst Dir iwwer CCA?

op 2024/04/26

Populär Posts

-

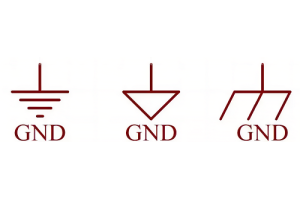

Wat ass d'GND am Circuit?

op 1970/01/1 2942

-

RJ-45 Connector Guide: RJ-45 Connector Faarfcode, Wiress Schemaen, R-J45 Uwendungen, RJ

op 1970/01/1 2501

-

Faser Connectorypen: SC VS LC an LC VS MTP

op 1970/01/1 2089

-

Stroum Oplëschtung vun Vendagen vun Eliminronik VCC, VDD, VE, VSS, a GND

op 0400/11/9 1895

-

Verglach tëscht DB9 an Rs232

op 1970/01/1 1765

-

Wat ass eng lr44 Batterie?

Elektrocizizieller, dee bulquitesch Kraaft, roueg provozéiert all Asft vun eisem Alldag, vun trivial Gadgeten zu Liewensgeldmoossname medizinesch Ausrüstung, se spillt eng stänneg Ausrüstung.Profau schafft Dir awer dës Energie, besonnesch, besonnesch hätt an aussergewéinlech ob effektiv se ass, ass keng einfach Aufgab.Et kënnt un dësen Hannergrond deen den Artikel ëmmer nach konzentréie...op 1970/01/1 1714

-

D'Fundamenter ze verstoen: Induktiounsbetrag, ankapaktanz

An der strenger Danzerkranzer vun elektrende Dometatiounsrooss, a gouf schëlleg Elementer Macetalen Elementer Maset Carriage Masistenz: Apraktik.All Barten vun all eenzeg Ziktiounen déi den dynamesche Rhythmus vum dynamesche Circulas diktéieren kënnen.Hei, mir stoppen sech un fir d'Klammen vun dëse Komponitiv ze entdecken, fir seng deieraarteg Insele benotzt an dat hannen-elektresch Indeels z...op 1970/01/1 1655

-

CR2430 Batterie ëmfaassend Guide: Spezifikatioune, Uwendungen an Vergréisserung zu CR2032 Batterien

Wat ass cr2430 Batterie?Virdeeler vun cr2430 BatterienNormierCr2430 Batterie UwendungenCr2430 EquivalentCr2430 vs cr2032Batterie Cr2430 GréisstWat fir ze kucken wann Dir de CR2430 an Equivalenten kaaftDateblat pdfOft gestallten Froen Batterien sinn d'Häerz vu klenge elektronesche Geräter.Zu de villenen verfügbaren sinn d'Coa Zellen eng primmesch Roll ze spillen, a Reiser, Beräich ze stellen.T...op 1970/01/1 1555

-

Wat ass rf a firwat benotze mir et?

Radio Frequenz (RF) Technologie ass e Schlësseldeel vu moderner Worklos Kommunikatioun, konstalléiert Daten Iwwerdroung iwwer laang Distanzen ouni kierperlech Statiounen ouni kierperlech Statiounen.Dësen Artikel läscht an d'Grondlage vun der RF, Erkläert wéi elektromagnetesch Stralung (EMR) mécht RF Kommunikatioun méiglech.Mir wäerten d'Prinzipien vun EMR erliichteren, d'Kreatioun a Kontr...op 1970/01/1 1541

-

Cr2450 vs Cr2032: Kann d'Batterie amplaz benotzt ginn?

Lithium magane Batterien hunn e puer Ähnlechkeeten mat anere Lithium Batterien.Héich Energie Dicht a laange Service d'Liewen ass d'Charakteristiken déi se gemeinsam hunn.Dës Zort Batterie huet d'Vertrauen an e Gonschten vu ville Konsumenten gewonnen wéinst senger eenzegaarteger Sécherheet.Deier Tech Gadgeten?Kleng Apparater an eisen Haiser?Kuckt ronderëm an Dir wäert se iwwerall gesinn.Ën...op 1970/01/1 1512